# **POWER SWITCH**

By Pierre Aloisi

Power Products

Senior Applications Engineer

Motorola Toulouse

This information has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Motorola reserves the right to make changes to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein. No license is conveyed under patent rights in any form. When this document contains information on a new product, specifications herein are subject to change without notice.

|  |  | • |

|--|--|---|

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

# **POWER SWITCH**

## **Preface**

In this work, it was my intent to try to answer some of many questions posed by power circuit designer about power semiconductors. A great deal of the information in this book is a direct result of the enormous amount of work and analysis conducted in the power products laboratory at Motorola, Toulouse, over the past five years.

In order to accomplish this task, i put together some of the latest developments in solid state physics as it applies to power components. In my opinion knowledge of new technologies is a key element in understanding the trade-offs in performance of the many devices that are available in todays market place. These technology developments form the base for the first section of the book. The second section, consisting of chapters 2 and 3, is a brief study of the various types of power semiconductor switches that are available today and how they interact with their environment. In the last section, we look at various factors that should be considered before chosing the proper power switch for a specific application.

A second book is planned for the near future which will feature the various applications for power switches.

Finally, I would like to thank all those anonymous inventors who have allowed me, through their pertinent questions, to discover so many things about power electronics.

I would also like to mention all the European Universities, Henri Foch, Pierre Rossel, Tore Underland... and their research teams who enlightened me with their contributions.

I wish to extend my thanks to all the engineers in the Motorola power semiconductor group, Phoenix and Toulouse for their help, their suggestions and advice.

## **TABLE OF CONTENTS**

|            |                                                                                                                                                                                                                                                           | Page                                                     |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| Section 1: | Physical properties of power devices                                                                                                                                                                                                                      |                                                          |

|            | Thermal resistance                                                                                                                                                                                                                                        | 1-3<br>1-19                                              |

| Section 2: | Various power switches                                                                                                                                                                                                                                    |                                                          |

|            | 1. Bipolar products 2. Power MOSfets 3. The MOS Thyristor 4. GEMfet 5. The Motorola power IC SMARTpower 6. The Thyristor                                                                                                                                  | 2-3<br>2-21<br>2-75<br>2-84<br>2-90<br>2-100             |

| Section 3: | Environment networks of bipolar transistors                                                                                                                                                                                                               |                                                          |

|            | <ol> <li>Base control of power transistors</li></ol>                                                                                                                                                                                                      | 3-3<br>3-27<br>3-33                                      |

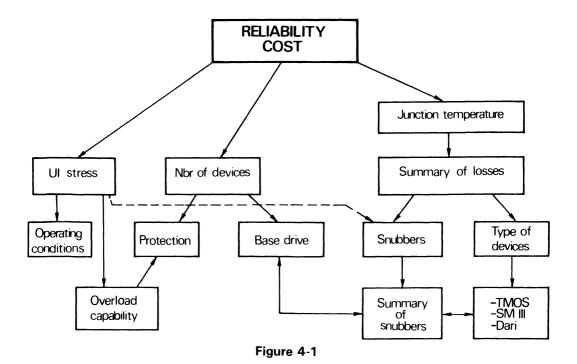

| Section 4: | Choice of power switch                                                                                                                                                                                                                                    |                                                          |

|            | 1. Introduction 2. Reliability 3. Costs 4. Voltage current features 5. Number of components 6. Junction temperature verses switching losses 7. Switching improvement circuit-snubbers 8. Types of power switch 9. The cases — Paralleling 10. Conclusions | 4-2<br>4-3<br>4-4<br>4-9<br>4-11<br>4-14<br>4-17<br>4-20 |

# Physical properties of power devices

# Section 1

#### **TABLE OF CONTENTS**

| 1. | The | ermal | resistance                                               | 1-3  |

|----|-----|-------|----------------------------------------------------------|------|

|    | A)  | Trans | sient thermal analysis of power components               | 1-3  |

|    |     | A-1.  | Introduction                                             | 1-3  |

|    |     | A-2.  | Definition of terms and units                            | 1-3  |

|    |     | A-3.  | Hypothesis                                               | 1-4  |

|    |     |       | A-3.1. Isothermic boundary surface                       | 1-4  |

|    |     |       | A-3.2. Adiabatic boundary surface                        | 1-5  |

|    |     | A-4.  | Graphic representation of asymptotes in logarithmic      |      |

|    |     |       | co-ordinates                                             | 1-5  |

|    |     | A-5.  | Multi layer system                                       | 1-6  |

|    |     | A-6.  | Real components                                          | 1-9  |

|    |     | A-7.  | Pulse response of semiconductor components               | 1-11 |

|    | B)  | Ther  | mal analysis for long pulses                             | 1-15 |

|    |     | B-1.  | Thermal parameters of transistors                        | 1-15 |

|    |     |       | B-1.1. Thermal resistance of chips                       | 1-15 |

|    |     |       | B-1.2. Thermal capacity                                  | 1-15 |

|    |     | B-2.  | Application of power                                     | 1-16 |

|    |     | B-3.  | The Radiator in ambient air                              | 1-17 |

|    |     |       | B-3.1. Radiation                                         | 1-17 |

|    |     |       | B-3.2. Free convection                                   | 1-17 |

|    |     |       | B-3.3. Forced convection                                 | 1-18 |

|    |     | B-4.  | Continuous use                                           | 1-18 |

| _  |     |       |                                                          | 1-19 |

| 2. |     | -     | rating areas                                             | 1-19 |

|    | A)  |       | and bias safe operating area                             | 1-19 |

|    |     |       | Introduction                                             | 1-19 |

|    |     |       | The first segment                                        | 1-19 |

|    |     |       | The second segment                                       | 1-20 |

|    |     | A-4.  | The fifth segment                                        | 1-20 |

|    |     |       | A-4.1. Two breakdown phenomena                           | 1-20 |

|    |     |       | A-4.2. For the standard emitter configuration we can say | 1 00 |

|    |     |       | that                                                     | 1-23 |

|    |     |       | A-4.3. Technological                                     | 1-23 |

|    |     |       | A-4.4. Temperature variation                             | 1-24 |

### **TABLE OF CONTENTS** (continued)

|    | A-5. Second breakdown                                    | 1-24 |

|----|----------------------------------------------------------|------|

|    | A-5.1. A thermal phenomenon                              | 1-25 |

|    | A-5.2. The avalanche injection                           | 1-30 |

|    | A-6. Thermal resistance at high voltages                 | 1-31 |

|    | A-7. Pulsed FBSOA                                        | 1-32 |

|    | A-7.1. Thermal limits                                    | 1-32 |

|    | A-7.2. Limits created by electric fields                 | 1-33 |

| B) | Switching safe operating areas                           | 1-34 |

|    | B-1. At turn off                                         | 1-34 |

|    | B-1.1. Electronic model                                  | 1-36 |

|    | B-1.2. Thermal model                                     | 1-38 |

|    | B-1.3. Generalization of model                           | 1-38 |

|    | B-1.4. Charges in secondary breakdown versus RBE and VBE | 1-39 |

|    | B-1.5. Critique of measuring this parameter              | 1-40 |

|    | B-2. Safe operating area                                 | 1-42 |

| C) | Overload safe operating areas                            | 1-43 |

|    | C-1. Olsoa 1                                             | 1-44 |

|    | C-2. Olsoa 2                                             | 1-44 |

|    | C-3. Bibliography                                        | 1-45 |

# Physical properties of power devices

# 1. Thermal resistance

#### A) Transient thermal analysis of power components

#### A-1. Introduction

The instantaneous temperature of a semiconductor junction is difficult to determine and is not normally used despite of its importance for reliable operation. For high power components this temperature can change very quickly, up to 106°C/sec, so that the mean temperature of the junction is entirely inadequate for measuring the safety margin of a given function.

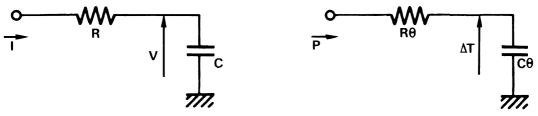

A technique using analysis of thermal and electrical conduction in an R.C. network has been perfected by W.E. Newell (1) and A. Fillatre (5).

This very practical and comprehensive method may be applied to a wide variety of situations.

It makes use of a graphic tool to evaluate the rise in temperature of a given material.

#### A-2. Definition of terms and units

Table 1-1

| Descriptions                                                  | Symbols   | Units   | Electric<br>analog symbol |

|---------------------------------------------------------------|-----------|---------|---------------------------|

| Increase in temperature                                       | ⊿t        | °C      | V                         |

| Power waste                                                   | P         | W       |                           |

| Thermal resistance                                            | R	heta    | °C/W    | R                         |

| Thermal capacity                                              | C	heta    | J/°C    | С                         |

| Thermal impedance                                             | $Z\theta$ | °C/W    | Zin                       |

| Transient thermal impedance Thermal response or step function | r(t)ΖΘ    | °C/W    | V/Is                      |

| Thermal conductivity                                          | K         | W/cm.°C |                           |

| Material density                                              | ρ         | g/cm³   |                           |

| Specific heat                                                 | ho        | J/g.°C  |                           |

| Material thickness                                            | е         | cm      |                           |

Thermal equations

Thermal resistance :  $R\theta = \frac{e}{k}$ Thermal capacity :  $C\theta = \frac{e}{k}\rho C$  (e.s.)= $\rho C$  Volume = C. weight

Table 1-2 - Thermal constants of electronic materials

|                                    | Steel | Aluminium | Copper | Silicon | Molybde<br>num | Eutectic | Pb Ag In | Mica<br>epoxy | AL2 03<br>alumine | Calme<br>air |

|------------------------------------|-------|-----------|--------|---------|----------------|----------|----------|---------------|-------------------|--------------|

| Density $ ho$                      | 7.75  | 2.70      | 8.85   | 2.33    | 10.22          |          | 11       | 3             | 3.7               | 13 10-4      |

| Thermal capacity C = J/g°C         | .45   | .90       | .39    | .75     | .27            | .3       | .13      | .84           | .85               | 1            |

| Thermal conductivity K = W/cm. ° C | .46   | 2.05      | 3.85   | .84     | 1.46           | 2.2      | .36      | .003          | .37               | 3 10-4       |

#### A-3. Hypothesis

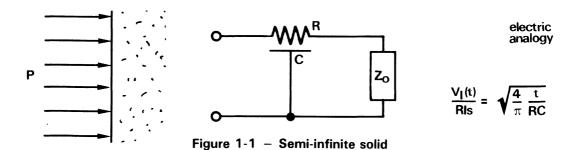

If a solid, semi-infinite center, unidimentional object is exposed to P amount of power the temperature rise at the surface of the solid object is given by:

$$\Delta T (t) = \left[ \frac{4}{\pi} \frac{t}{k\rho c} \right]^{\frac{1}{2}} P \tag{1}$$

t is measured from the moment that P is applied.

For plates of finite thickness e, formula (1) may be used for "short duration pulses" (see later) otherwise 2 possible cases exist for the equilibrium condition.

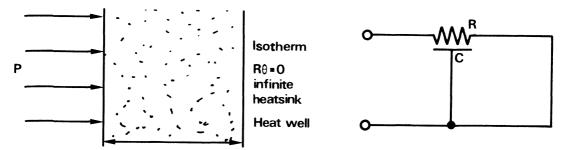

A-3.1. Isothermic boundary surface, the temperature rise  $\Delta T(t)$  asymptotically approaches the equilibrium state and can be expressed as follows:

$$\Delta T (t) = \frac{e}{k} P$$

(2)

with  $e/k = R\Theta$  (thermal resistance of material).

An analogy can be made to an electrical circuit with a distributed impedance and a short circuit.

Figure 1-2 - Solid with finite e thickness and infinite heatsink.

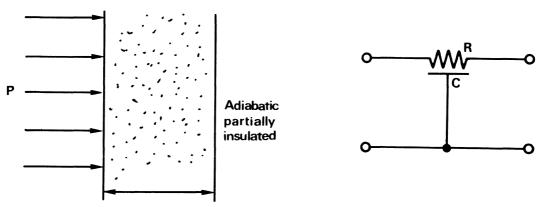

#### A-3.2. ADIABATIC BOUNDARY SURFACE

We obtain: for large value of t  $\Delta T$  (t) =  $\frac{t}{\rho Ce}$  P (3)

Figure 1-3 - Solid with finite e thickness and mounted on an insulated surface

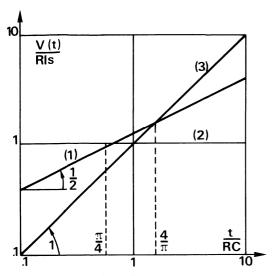

### A-4. Graphic representation of asymptotes in logarithmic co-ordinates

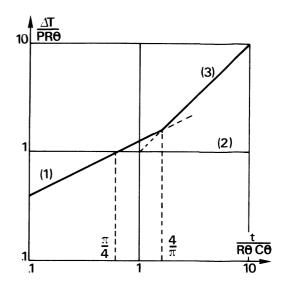

If V1(t) / RIs is represented in terms of time t/Rc we get for each of the 3 study cases:

- semi-infinite solid line terminated on its characteristic impedance

- solid terminated on a heat sink, line short circuited

- solid terminated on a thermal insulator, open line

The following asymptotes:

The intersections of the asymptotes by temperature rises in terms of time defines the "Thermal Transient Times".

In second case: isotherm, we have:

$$\tau 1 = \frac{\pi}{4} \frac{\rho c}{k} e^2$$

(4)

In the third case: adiabatic, we have:

$$\tau 2 = \frac{4}{\pi} \frac{\rho c}{k} e^2$$

(5)

Figure 1-4 — Representation of asymptomes for equivalent electrical circuits

Figure 1-5 - Thermal asymptotes

If t <  $\tau$ 1 and the material is semi-infinite formula (1) is used, if t >  $\tau_1$  and the material is connected to an infinite heat sink formula (2) is used, if t >  $\tau$ 2 and the material is connected to an insulating surface formula (3) is used.

#### A-5. Multi layer system

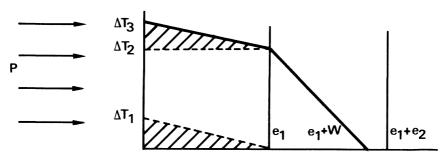

Figure 1-6 - Multi layer system

If a material has a constant temperature gradient, then the quantity of heat introduced during time t is equal to: Q = Pt.

This quantity is proportional to the area of the bottom shaded triangle in Figure 1-6.

$$\alpha \left(\frac{1}{2}\Delta T_1 e_1\right) = Pt$$

The lpha equivalent factor to make the formula homogeneous is equal to  $ho_1$  C  $_1$  giving:

$$\frac{1}{2}\Delta T_{1}\rho_{1}C_{1}e_{1} = Pt$$

This can also be written for a stabilized linear system on a heatsink, as:  $\Delta T_1 = \frac{P}{k_1} e_1$ eliminating e<sub>1</sub> we get:  $\Delta T_1^2 = \frac{2t}{k_1 \rho_1 c_1} P2$  or  $\Delta T_1 = \left[ \frac{2t}{k_1 \rho_1 c_1} \right]^{1/2} P$ (6)

The thermal transient time is defined for  $\tau = t$  when the propagation front reaches the

heat sink as:

$$T = \tau = \frac{1}{2} \frac{\Delta T_1}{P} \rho_1 c_1 e_1 = \frac{1}{2} \frac{\rho_1 c_1}{k_1} e_1^2$$

(7)

If there is an e<sub>2</sub> non isothermic layer, it may be written as:  $\Delta T_3 = \Delta T_2 + \Delta T_1 = \Delta T_2 + \frac{P}{k_1} e_1$ with  $\Delta T_2 = \frac{P}{k2} W$

The heat quantity introduced is at time  $t > \tau$  1

area of second layer triangle  $\frac{1}{2}\Delta T_2 w$

+ area of rectangle, first layer  $\Delta T_2 e_1$

+ area of triangle, first layer  $\frac{1}{2} \Delta T_1 e_1$

So that: Pt =  $\frac{1}{2} \rho_2 C_2 W \Delta T_2 + \rho_1 c_1 e_1 \Delta T_2 + \frac{1}{2} \Delta T_1 e_1 \rho_1 c_1$

If we write

$$\tau$$

(1 + 2) as the first and second layer thermal transient time, we get  $W=e_2$ , ie:  $(\frac{1}{2} \, \rho_2 \, c_2 \, e_2 + \rho_1 \, c_1 \, e_1) \, \frac{e_2}{k_2} \, P + \frac{1}{2} e_1 \, \rho_1 \, c_1 \, \frac{e_1}{k_1} \, P = P \, (\tau \, 1 + 2) \, \text{ with } \Delta T_2 = \frac{P}{k_2} \, e_2 \, , \, \, \Delta T_1 = \frac{P}{k_1} \, e_1$

Therefore:

$$\tau 1 + 2 = \frac{1}{2} \frac{\rho_1 c_1}{k_1} e_1^2 + \frac{1}{2} \frac{\rho_2 c_2 e_2^2}{k_2} + \frac{\rho_1 c_1 e_1 e_2}{k_2}$$

(8)

When the propagation front reaches the heat sink, we have the equilibrium state for which:  $\frac{\Delta T}{P} \infty = \frac{e_1}{k_1} + \frac{e_2}{k_2}$

$$\tau 1 + 2 + 3 = \frac{1}{2} \frac{\rho 1^{c_1}}{k_1} e_1^2 + \frac{1}{2} \frac{\rho 2^{c_2}}{k_2} e_2^2 + \frac{1}{2} \frac{\rho 3^{c_3}}{k_3} e_3^2 + \frac{\rho 1^{c_1} e_1 e_2}{k_2} + \frac{\rho 1^{c_1} e_1 e_3}{k_3} + \frac{\rho 2^{c_2} e_2^2 e_3}{k_3}$$

(9)

with a heat sink, one could write  $\frac{\Delta T}{P} \infty = \frac{e_1}{k_1} + \frac{e_2}{k_2} + \frac{e_3}{k_2}$  for greater accuracy and consistancy of

the Newell concept, the factor  $\frac{4}{\pi}$  should be substituted for the factor 2 in equations (7) (8) and (9).

In general for an i-layer system, the total transfer time on a heat sink is.

$$\tau 1 + \dots i = \sum_{o}^{i} \left[ \frac{\pi}{4} \frac{\rho i \operatorname{ci} \operatorname{ei}^{2}}{\operatorname{ki}} + \frac{\operatorname{ei}}{\operatorname{ki}} \sum_{o}^{i-1} \rho_{i} \operatorname{e}_{i} \operatorname{c}_{i} \right]$$

(10)

and its preceding time is known  $\tau + ... - 1$  one can write:

$$\tau 1 + ... i = \tau i + ... i - 1 + \frac{\pi}{4} \rho_i c_i \frac{e_i^2}{k_i} + \frac{e_i}{k_i} \sum_{j=1}^{i-1} \rho_j e_j C_i$$

To construct an asymptotic diagram representing the temperature changes a of multilayer system with power applied you simply calculate:

1) the combined transient times:

$$\tau 1$$

,  $\tau 1 + 2$ ,  $\tau 1 + 2 + 3$ , ...

corresponding to the interfaces of the various levels.

2) the combined thermal resistances:

$$\frac{e_1}{k_1}$$

,  $\frac{e_1}{k_1}$  +  $\frac{e_2}{k_2}$ ,  $\frac{e_1}{k_1}$  +  $\frac{e_2}{k_2}$  +  $\frac{e_3}{k_3}$ ,....

these points define the "breakpoints" of an asymptotic diagram in logarithmic coordinates.

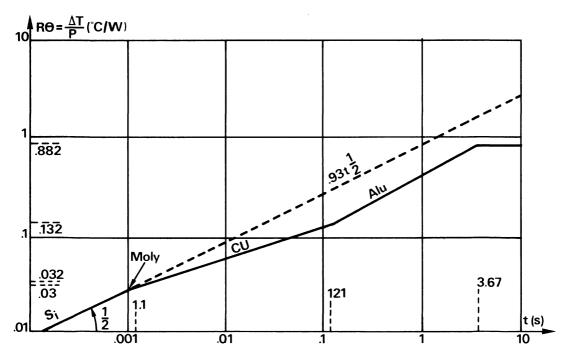

Table 1-3 - Example

|            | e <sub>(cm)</sub> | e/k  | $\frac{\pi}{4} \frac{\rho c}{k} e^2$ (ms) | $\frac{e_{i}}{k_{i}}\sum_{o}^{i-1}\rho_{i}c_{i}e_{i}$ | Στ    |

|------------|-------------------|------|-------------------------------------------|-------------------------------------------------------|-------|

| Silicon    | .025              | .03  | 1                                         |                                                       |       |

| Molybdenum | .003              | .002 | .005                                      | .1                                                    | 1.105 |

| Copper     | .4                | .1   | 110                                       | .45 + 10                                              | 121.6 |

| Aluminium  | 1.5               | .75  | 2500                                      | 1000 + 7 + 40                                         | 3668  |

Figure 1-7 - Thermic stacking of a semiconductor

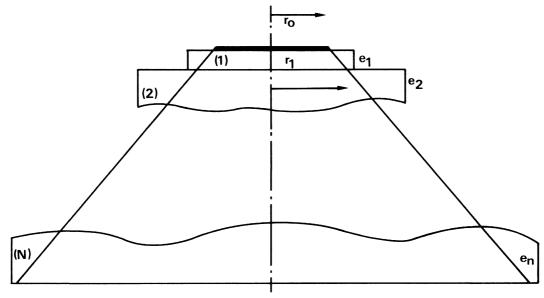

#### A-6. Real components

The hypothesis of the unidimensionality of heat flow is only valid if the thermal penetration is minimal relative to the lateral dimensions of the active area. A significant improvement in accuracy can be obtained by assuming that the heat flows in a "truncated cone" having a 45° angle at the top, per Figure 1-8.

Figure 1-8 - Heat diffusion in "truncated cone"

For each layer in a multi-layer system, we can define an area S', a thermal conductivity K'I and a specific heat C'I and for any layer I we can write:

RTHI =

$$\frac{1}{\text{KI}} \int_0^{\text{EI}} \frac{dx}{\text{area}}$$

with Areas =  $\pi \left[ r_{\text{I}-1} + x \right]^2$  for a circle

=  $\left[ a + 2x \right]$  for a square with side a

=  $\left( a + 2x \right) \left( b + 2x \right)$  for a rectangle sides a and b

so: RTHI circle =

$$\frac{1}{k_{\parallel}\pi} \frac{e_{\parallel}}{r_{\parallel -1} (r_{\parallel -1} + e_{\parallel})}$$

RTHI square =  $\frac{1}{k_{\parallel}} \frac{e_{\parallel}}{(a_{\parallel -1} + 2e_{\parallel})} a_{\parallel -1}$  RTHI rectangle =  $\frac{1}{k_{\parallel}} \frac{1}{2(a_{\parallel -1} - b_{\parallel -1})} \operatorname{Ln} \left(\frac{a_{\parallel -1}}{b_{\parallel -1}}\right) \left(\frac{2e_{\parallel} + b_{\parallel} - 1}{2e_{\parallel} + a_{\parallel} - 1}\right)$

Equating (rI-1) for the circle to the diameter  $r_0$  of the active surface, we have:

$$rl-1 = ro + e1....+el-1$$

For the square, we have:  $al-1=a+2e_1+2e_2....+2e_{l-1}$

The thermal conductivity K'I of the equivalent layer is:

RTHI =

$$\frac{1}{K'I} \frac{el}{\pi ro^2}$$

Thus K'I for me circle =  $\frac{1}{RTH} \frac{el}{\pi ro^2}$  = KI  $\frac{(ro + ...el - 1)(ro + ...el)}{ro^2}$

It follows that based on the total transient response time we have:

$$C'I = \frac{k'I}{kI}CI$$

or K'I square =  $\frac{1}{RTH} \frac{el}{a2} = \frac{kI (a+2el...2el-1) (a+...2el)}{a^2}$

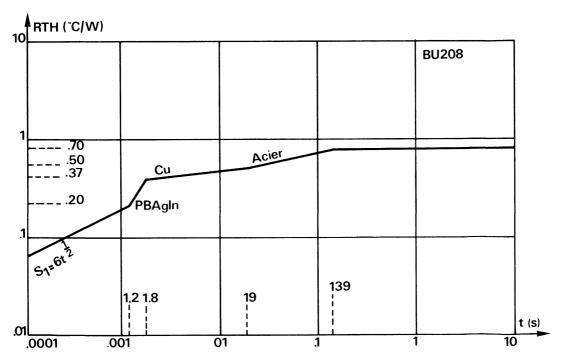

As an example, let us consider the Motorola BU208, a bipolar transistor with square active surface of  $S' = 14 \times 10^{-2}$  cm<sup>2</sup>.

Table 1-4

|          | e <sub>cm</sub>      | k′   | C'= <u>k</u> 'c | e/k′s′ | R $\theta$ | $\frac{\pi}{4} \frac{\rho c}{k} e^2 ms$ | $\underbrace{ei}_{ki} \sum_{o} i-1 \rho_i c_i e_i$ | τi ms |

|----------|----------------------|------|-----------------|--------|------------|-----------------------------------------|----------------------------------------------------|-------|

| Silicon  | 275×10 <sup>-4</sup> | .95  | .85             | .2     |            | 1.2                                     |                                                    | 1.2   |

| Pb Ag In | 40×10 <sup>-4</sup>  | .475 | .17             | .17    | .37        | .05                                     | .5                                                 | 1.8   |

| Copper   | .15                  | 8.5  | .86             | .13    | .50        | 16.0                                    | 1.1                                                | 19    |

| Steel    | .15                  | 4.15 | 2.28            | .26    | .76        | 76                                      | 44                                                 | 139   |

Figure 1-9 - Asymptotic diagram of thermal resistance of BU208

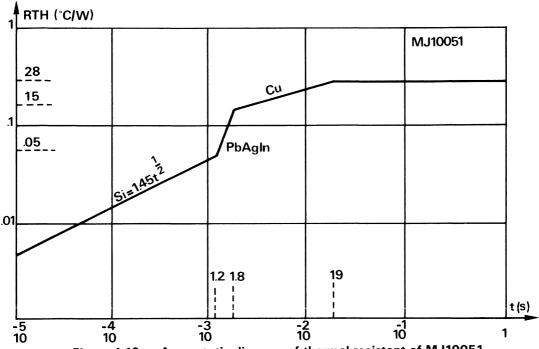

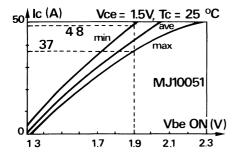

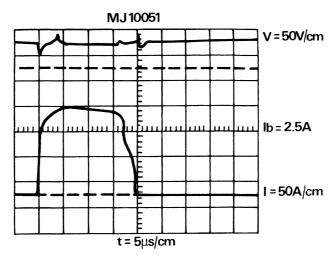

If we now consider the MJ10051 in the high current package (case 346): this device has four parallel chips mounted on a copper heatsink, 1.5 mm thick.

We can take the preceding table, looking at copper, and apply a corrective factor of 4 given that the active surface of an MJ10051 chip is equal to that of a BU208 silicon = .05 and PbAgIn = .10 and the copper = .13.

Transient times are identical to previous ones as they include only the physical parameters of the material and the thickness of the components which are identical. The silicon

curve is

$$\frac{1}{A}\sqrt{\frac{4}{\pi}} \frac{1}{.95.85 \times 2.3} t^{\frac{1}{2}} = 1.45t^{\frac{1}{2}}$$

which is the first section of the complete curve for the MJ10051 as shown below:

Figure 1-10 — Asymptotic diagram of thermal resistant of MJ10051

#### A-7. Pulse response of semiconductor components

#### A-7.1. A SINGLE POWER PULSE

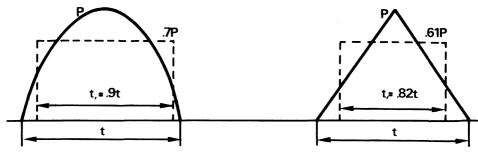

There are many situations where a non-rectangular power pulse may need to be converted to an equivalent rectangular pulse in order to analyze the thermal response.

For waveforms that can be expressed as a simple function such as the sinusoidal and triangular waveforms shown in Figure 1-11. The effective value can be used for the height of the rectangular equivalent. Then by setting the area of the non-rectangular waveform equal to the area of the equivalent rectangular waveform.

The width of the equivalent waveform can be determined as shown below in a) and b).

#### A-7.1.1. For the sinusoïd, effective value is:

$$Prms = -707 Ppeak$$

The area under the sinusoïd is  $2/\pi = 0.636$ , setting this equal to the area under the equivalent rectangular waveform gives 0.636 = (0.7P)t, and then solving for

$$t_1 = \frac{0.636}{0.707} = 0.91 t$$

Figure 1-11 - Normalized power pulses

A-7.1.2. For the triangular waveform, a worst case analysis would result by assuming that the triangular waveform can be expressed as a  $\sin^2$  function. Since the area under the  $\sin^2$  function is 1/2, and the effective value  $\sqrt{3/8}$  or  $\sim$  0.61, the eight of the equivalent rectangular waveform would be .61P while the width would be t,  $t_1 = \frac{0.50}{0.61} = .82t$

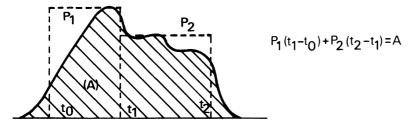

A-7.1.3. For a complex pulse the rectangular equivalent can be approximated. By added a series of smaller rectangular equivalents as shown in Figure 1-12.

Figure 1-12 - Model for complex power pulse

With the power pulse converted to an equivalent rectangular pulse the temperature rise can now be calculated from  $\Delta T = P$  (transient R).

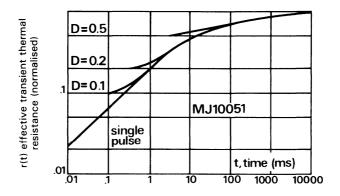

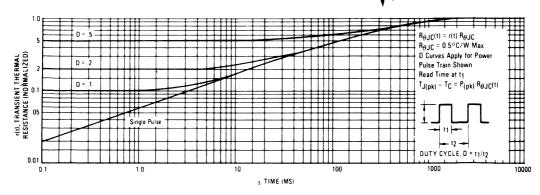

Transient R for the equivalent rectangular pulse can be found from the curves that were developed in this section (i.e. Figure 1-9). Most manufacturers publish normalized curves as shown in Figure 1-13 which is conjunction with  $R\Theta_{JC}$  as follows:

Figure 1-13 - Normalised thermal response of MJ10051

$$\Delta T = PR\Theta$$

jc r(t)

For this example, if  $P = 25 \text{ A} \times 600 \text{ V} = 15000 \text{ W}$  for 10 microseconds:

Then  $\Delta T = 15000 \times 0.25 \times 0.02 = 75$  °C

i.e.:

$$Tj = \Delta T + TA = 75 + 25 = 100$$

°C.

It is generally accepted that for pulses significantly below steady state conditions and low duty cycles that the temperature decrease in the same manner in which it increased.

#### A-7.2. A SERIES OF POWER IMPULSES.

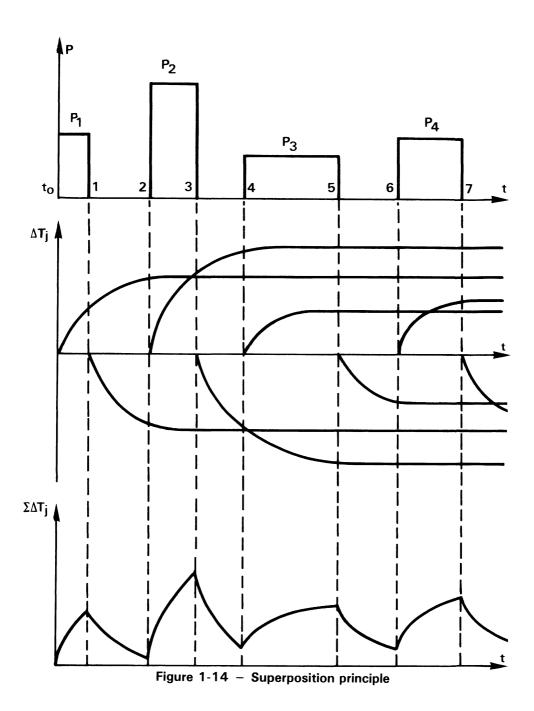

A-7.2.1. Random pulses. For a series of random pulses the **superposition** principle is applied which supposes that the cooling down of a product follows the same laws as its heating, the junction temperature after a series of pulses is the algebraïc sum of preceding heating and cooling cycles (see Figure 1-14).

This method can be applied when the total time of heating is less than the time to reach steady state.

We get:  $\Delta T_1 = P_1 r(t1) R\Theta_i C$

$$\Delta T_3 = \left[ P_1 r(t3) - P_1 r(t3 - t1) + P_2 r(t3 - t2) \right] R\Theta_j C$$

(12)

$$\Delta T_5 = [P_1 r(t5) - P_1 r(t5 - t1) + P_2 r(t5 - t2) - P_2 r(t5 - t3) + P_3 r(t5 - t4)] R\Theta_{i}C$$

Generally the last 3 pulses only influence junction temperature at moment t (3rd pulse).

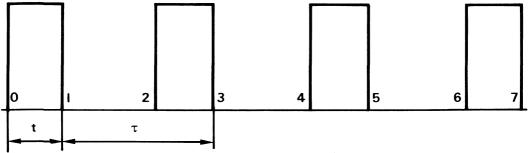

#### A-7.2.2. Pulses equal in size and length: uniform pulse series.

General cases: - at the end of the 1st pulse, as for a single pulse

- at the end of one impulse, in a stabilized state  $\Delta T_i = PR\Theta c r(t_1D)$

On Figure 1-12, we can read off the desired duty cycle condition, for example  $\delta = 0.5$  for t = 1 ms gives us r(t<sub>1</sub> D) = .5 and we have  $\Delta T_i$  = .5 x .25 x P so .125 P

If we assume Tjmax = 150 °C and T ambient = 25 °C, we get P = 1000 W i.e. double the nominal power capability of the product, which is normal for pulsed conditions of 50%. We can obviously use the superposition principle but calculations are longer.

#### Special cases

Using average power to find the temperature at the end of the n+1 pulse, we get:

$$\Delta T_{n+1} = \left[\frac{t}{\tau} r \left(t_{2n-1}\right) + \left(1 - \frac{t}{\tau}\right) r \left(1 + \tau\right) + r(t) - r(\tau)\right] P_D \; R\Theta_j C$$

Assuming that PD = 500 W, R $\Theta$  JC = .25 (MJ10051) $\Delta$ t = width of pulse = 5 ms, period  $\tau$  = 20 ms and if we want to find the tenperature at the end of the 5th pulse, we have:

$$n+1=5$$

$n=4$   $2n-1=7$

t2n - 1 = t7 = 65 ms.

On the curve (Figure 1-13) we have: r(65) = .70

$$r(25) = .6$$

$r(5) = .4$   $r(20) = .55$

i.e.:

$$\Delta \text{Tn} + 1 = \begin{bmatrix} \frac{5}{20} (0.70) + (1 - \frac{5}{20}) 0,60 + 0,40 - 0,55 \end{bmatrix} 500 \times .25$$

$$= 125 [0,14 + 0,45 + 0,4 - 0,55] = 56 ^{\circ}\text{C}$$

Figure 1-15 - Pulse series

If formula 12 was used we would obtain:

$$\Delta T5 = [r(85) - r(80) + r(65) - r(60) + r(45) - r(40) + r(25) - r(20) + r(5)] 500 \times .25$$

$125(0,00 + 0,01 + 0,02 + 0,04 + 0,4) = 0.47 \times 125 = 59$  °C

Both formula can thus be used.

#### B) Thermal analysis for long pulses

#### B-1. Thermal parameters of transistors

#### **B-1.1. THERMAL RESISTANCE OF CHIPS**

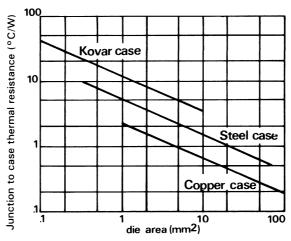

As we have seen, thermal resistance of the chip in relation to the case is a function of the area of the chip and of the material on which it is mounted, this can then be seen in Figure 1-16 as a function of the die area:

Figure 1-16 - Thermal resistance of chips

#### **B-1.2. THERMAL CAPACITY**

The thermal capacities of various cases are given in the table below. Remember that this was calculated using the formula:

$$C\theta = weight \times C$$

Table 1-5

|                                         | Aluminium | Steel | Copper | Copper<br>High current package<br>Case 346 Motorola |

|-----------------------------------------|-----------|-------|--------|-----------------------------------------------------|

| Weight (g)                              | 7         | 12    | 15     | 50 g copper<br>50 g epoxy                           |

| Thermal capacity $C\theta: J/^{\circ}C$ | 6.3       | 5.4   | 5.6    | 20 + 30 =<br>50                                     |

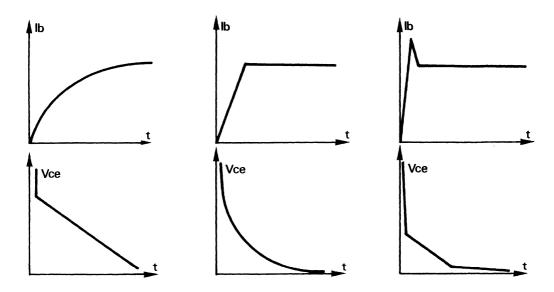

#### B-2. Application of power

When power is applied, the thermal system operates like the equivalent electrical system (see paragraph B-1.).

Figure 1-17 - Thermal analogy

Therefore the curves shown in Figure 1-18 can be drawn to simulate the thermal response of the system.

Figure 1-18 - Response to a step function

Example: the thermal capacity of the Motorola high current package from the previous table is =  $C\theta = 20 + 30 = 50 \text{ J/°C}$ .

The thermal resistance of the MJ10051 is  $0.25\,^{\circ}$  C/W and one time constant for this device on an infinite heatsink can be found from:  $\tau = R\theta C\theta = .25 \times 50 = 12.5$  seconds The curve in Figure 17 has as its equation:  $\Delta T = \Delta T_m (1 - \exp{\frac{-t}{\tau}})$

So, we can say that when we apply a power step to this product, its temperature will rise to 60% of its equilibrium temperature in 12.5 seconds.

If we wished to know the time required to obtain 99.9% of its equilibrium temperature, we would need:

$$\frac{\Delta T}{\Delta Tm}$$

= .999=1-exp  $\frac{-t}{12.5}$  or exp  $\frac{-t}{12.5}$  = .001 or  $t$  = -12.5 Log .001  $t$  = -29 (-3) = 87 seconds

It takes about 87 seconds for this device to reach its thermal equilibrium condition. For cooling we have the same relationship:  $\Delta T = Tm (e^{-t/\tau})$

If we wanted to know the time required to return to 1% of ambient we calculate as follows:  $0.01 = (exp \frac{-t}{12.5})$  t = -29 Log 0.01 = 58 seconds

#### B-3. The radiator in ambient air

Dispersion of calories can be done in 3 different ways:

- conduction (already seen)  $R\Theta = e/k$

- radiation and

- convection

#### **B-3.1. RADIATION**

The rate of calory-transfer by given area can be found using the STEPHAN-BOLTZMANN law (13)  $_{HR=6.10}$  –12  $_{E}$  (TB<sup>4</sup> – TA<sup>4</sup>) in W/cm<sup>2</sup>.  $_{C}$  (13)

TB and TA = temperature of radiant surface and ambient in °C.

E being emissivity (see following Table 1-6).

Table 1-6

| Material                                                                                                                            | E                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| Anodized aluminium Polished aluminium Polished copper Oxidized copper Oxidized steel Oil paint (any color, varnish) Alumine (white) | 0,7 - 0,9<br>0,05<br>0,07<br>0,7<br>0,7<br>0,9<br>0,9 |

For example: a TO3 of E = 0.9 and TB = 100 °C TA = 40 °C HR  $\approx 610^{-4}$  W/cm<sup>2</sup> °C

#### **B-3.2. FREE CONVECTION**

The following equation gives us the transfer coefficient in calm air at sea level up to a

temperature of 800°C:

$$H_C = 4.10^{-4} \left(\frac{\Delta T}{L}\right)^{\frac{1}{4}} \text{ in W/cm}^2.$$

°C (14)

L being the length of the vertical part of radiator,  $\Delta T$  the difference of temperature between the surface and ambient air.

For example, a vertical TO3 (L = 2.5 cm) of temperature =  $100^{\circ}$ C, in calm air at  $40^{\circ}$ C, gives us:  $H_C = 10^{-3}$  W/cm<sup>2</sup>. °C

#### **B-3.3. FORCED CONVECTION**

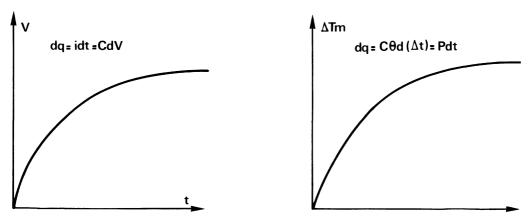

The general formula is written as:  $H = 2.10^{-2} \sqrt{\frac{v}{L}}$  with v = airspeed in m/seconds, L in cm. The thermal resistance convection curve verses air speed is shown in Figure 1-19.

From this curve, we can see that air moving at 6 m/s is sufficient to reduce thermal resistance by a ratio of about 10 to 1.

We can consider then, that convection plays and important part in heat transfer.

In free air heat is transfered at 70% by convection and 30% by radiation, as soon as ventilation is included, the radiation part drops to about 2% the total. A since convection is a more efficient means of heat transfer, the temperature of the device being cooled decreased significantly. Figure 1-20 shows the relationship between convection heat transfer and altitude, another factor that may need to be considered when analyizing a thermal system.

#### B-4. Continuous use

The thermal resistance of a TO3 can be calculated in free air as follows:

$$R_{CA} = \frac{1}{(HC + HR) \times \text{area } \times 2 \text{ sides}} = \frac{1}{10 - 3 \times 6 \times 2} = 40 \text{ °C/W}$$

Its thermal capacity being 6J/°C (from II-A-2), we get R $\Theta$ C = 240. The formula for its thermal resistance is  $R\Theta$ JA = 40 (1-exp  $\frac{-t}{240}$ )

Example = assume a 180 W pulse is applied for 1 second to a TO3 device, what is its temperature rise at the end of 1 second?  $\Delta T = \frac{P}{C\theta} = \frac{180}{6} = 30 \, ^{\circ}\text{C}$

If we want the time required for the case to return to ambient temperature + 1 °C when the power pulse is removed we have:  $\Delta T = \Delta T m exp$   $\frac{-t}{240} = 30 exp$   $\frac{-t}{240} = 1$

or  $t = 240 \text{ Ln } 30 \text{ or } 550 \text{ log } 30 = 550 \times 1,477 = 820 \text{ seconds.}$

An identical calculations for the high current case (C346) MJ10051 is as follows:

$$RC\theta = \frac{10^3}{3 \times 25 \times 2} = 6 \text{ °C/W}$$

in free air

the thermal capacity of this case is  $C\theta = 50 \text{J/°C}$  (Paragraph II-A-2) therefore  $R\theta$   $C\theta = 6 \times 50 = 300$  seconds resulting in the general equation  $R\theta_j A = 6$  (1-exp  $\frac{-t}{300}$ )

# 2. Safe operating areas

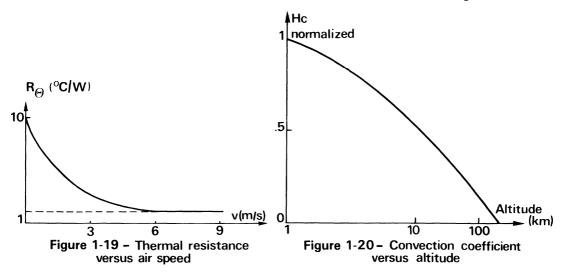

#### A) Forward bias safe operating area (SOA or FBSOA)

#### A-1. Introduction

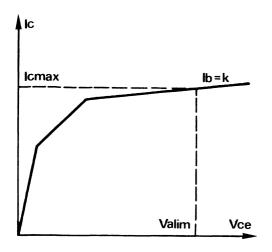

This area is limited, in general, by 4 straight segments on log  $\times$  log  $\vee$  graph (see Figure 1-21).

Figure 1-21 - Typical FBSOA

**A-2.** The first straight segment (1), parallel to the voltage axis, gives us a continuous current limit, typically this limit is based on limiting the current density in the bonding wires to a specific level. However in some cases the device chip size may be the limiting factor. The military specification MIL38510 specifies the maximum current density for bonding wires with the following relationship.  $I = Kd^{3/2}$  (1) Where d is equal to the wire diameter in millimeters.

K depends on the type and length of the wires. Values for various materials are shown in Table 1-7.

Table 1-7

|           | L<1mm<br>K | L>1mm<br>K |

|-----------|------------|------------|

| Aluminium | 171        | 118        |

| Gold      | 234        | 160        |

| Copper    | 234        | 160        |

| Silver    | 117        | 82         |

| Others    | 70         | 48         |

The information in Table 1, and equation (1) can be used to determine that an aluminium wire of 10 mils in diameter (0.25 mm) and a length of over 1 millimeter would take a continuous maximum current of:  $I = 118 \times 0.25 \frac{3}{2} \approx 15A$

A-3. The second segment (2) on the SOA curve is the D.C. Power dissipation limit.

P=VI=constant, represents this segment on the SOA curve.

This maximum power is limited to a level which will satisfy this relationship:  $T_{j_{max}} = P. R\theta_{j} - c$

Tjmax is the rated junction temperature defined for reliable operation.  $R\theta$  jc being junction-case thermal resistance which is a function of chip size and case materials. For this portion of the SOA curve the temperature gradient is homogeneous across the entire chip. At higher voltages the electric field can produce a non-homogeneous temperature gradient and effectively reduce the power handling capability of the device. This situation exists for segments 3 and 4 and will be discussed next.

A-4. An analysis of segment 4 will help to explain segment 3. Therefore segment 4 will be looked at first.

A-4.1. Two breakdown phenomena can expect for segment 4.

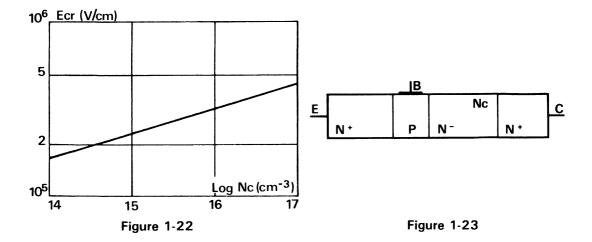

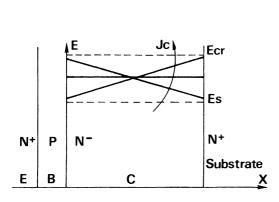

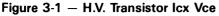

A-4.1.1. In the presence of a strong electric field, the carriers may have enough energy from the network atoms to free other carriers, these, in turn generate other electron – hole pairs and we get a multiplying phenomenon right up until the device avalanches. This phenomenon is reversible. The field limit Ecr is a function of the doping of the lightly doped collector zone (Figure 1-22).

Figure 1-22 — Field limit Ecr versus collector doping density.

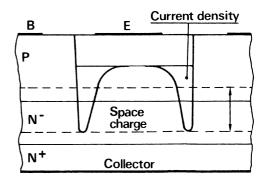

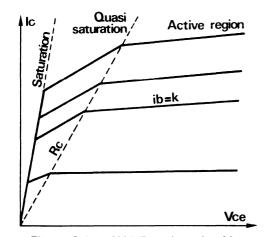

Figure 1-23 — Represents an NPN high voltage power transistor.

Figure 1-24 — Electric field at BC junction

Figure 1-25 — Miller factor versus V/Vb

Which develops in the lightly doped region of the collector, Figure 1-24, also represents

Poisson's equation:

$$\frac{dE}{dx} = \frac{1}{\epsilon} (qNc - \frac{Jc}{v})$$

(2)

$v = being the speed of the carriers (<math>v = \mu_0 \epsilon$ )

Jc = the current density

$\mu$  = carrier mobility

$\epsilon$  = electric field

If we consider the phenomenon at low currents, we can say  $\frac{dE}{dx} = \frac{1}{\epsilon} q Nc$

Since Nc is practically constant for an epitaxial transistor dE/dx is constant as indicated in Figure 1-24. The voltage supply is proportional to the area under the straight line dE/dx.

If we increase the supply, the dE/dx line will rise up to the Ecr field limit and create an avalanche or first breakdown.

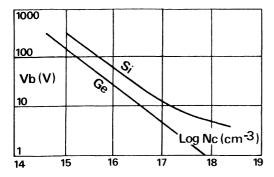

The multiplying avalanche factor has been stated by Miller in the following formula:

$$M = \frac{1}{1 - \left(\frac{V}{VB}\right)^m}$$

V = voltage supply

$V_B$  = avalanche voltage

m = multiplying factor depending on material

Table 1-7

| Semiconductors       | N<br>Type | P<br>Type |

|----------------------|-----------|-----------|

| Silicon<br>Germanium | 4         | 2         |

| Germanium            | 3         | <u> </u>  |

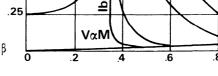

The M variations with V/VB m are shown in Figure 1-25.

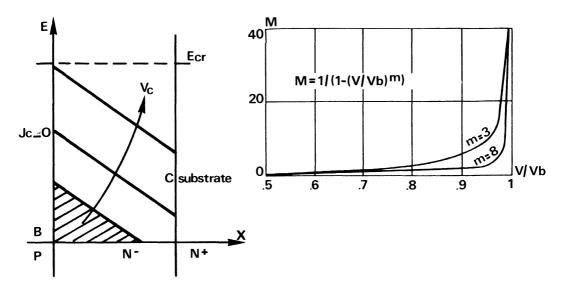

The value of VB depends on the material and technology of the junction.

For an abrupt junction, Figure 1-26 applies.

1000 Vb(V) 10 Log a 18 19 20 21 22 23

Figure 1-26 — Avalanche voltage versus material

Figure 1-27 — Diffusion curve slope

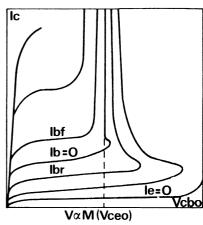

For graduated junctions (triple diffused technology), Figure 1-27 applies. The general equation for total transistors collector current is:  $I_C = M (\alpha I_E + I_{CB})$  ICB being the reverse diffusion current in volume or charge regenerator.

If we write IE = IC + IB we have:  $IC = \frac{M}{1 - \alpha M}$  (ICB +  $\alpha IB$ )

For the avalanche  $\alpha M > 1$ , the base current reverses itself and becomes IBR, giving:

$$Ic = \frac{ICB - \alpha IBR}{1 - \alpha (VCE/Vs)^{m}} \quad \text{or again} \quad VCE = VB \quad \left\{ 1 - \alpha + \alpha \left[ \frac{IBR}{IC} - \frac{ICB}{IC} \right] \right\} \quad 1/m$$

(4)

This equation does not take into account the possible reverse current from the emitter. When IC increases compared to IBR, we can write:

VCE+VB

$$(1-\alpha)^{1/m}$$

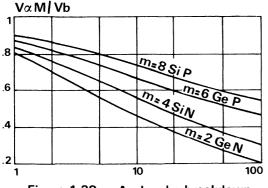

setting VCE=V $\alpha$ M gives V $\alpha$ M = VB  $(\beta+1)^{1/m}$  (5)

.75

.5

Ic/Icb

lb=0

which is graphically represented in Figure 1-28.

Figure 1-28 — Avalanche breakdown versus gain

Figure 1-29 — Avalanche characteristics

le = O

lbr=20 lcb

The reference material is the lightly doped region of the collector (N-) or drift zone. A graphic representation of the avalanche characteristics are shown in Figure 1-29. If the actual depth of the N- region is made small, the breakdown voltage decreases proportionally from the following relationship:

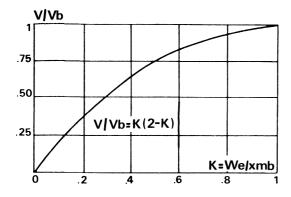

BVCBO =  $\frac{\text{We}}{\text{xmB}}$   $\left(2 - \frac{\text{We}}{\text{xmB}}\right)$ VB xmb being the minimum depth of the N- region to sustain VB. We:being the actual N- region depth.

Figure 1-30: Is a graphical representation of this relationship.

Figure 1-30 — Breakdown voltage versus collector depth

Figure 1-31 — Avalanche breakdown curves

A-4.1.2. If N-region is sufficiently spread and the base region is highly resistive with its Wb thickness thin emitter collector punch trough Vpt occurs when the electric field sufficiently affects the emitter base function prior to avalanche.

At this moment the breakdown voltage of the transistor is limited by Vpt instead of VB.

A-4.2. For the standard emitter configuration we can say that BVCES = BVCBO. If the device is limited by the avalanche then BVCES = BVCBO - BVEBO, if punch through is the limiting factor then:

BVCES = BVCBO - BVEBO = VpT. For the BVCEO we have:

BVCEO=

$$V\alpha M = \sqrt{\beta}$$

(7)

if the device is not limited by VpT, the curves shown in Figure 1-31, apply.

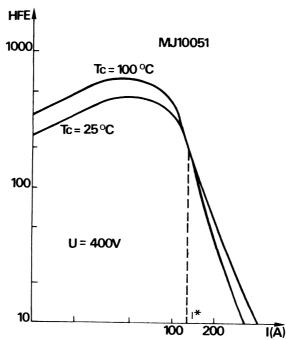

#### A-4.3. TECHNOLOGICAL COMPROMISES

We know that VCEOsus = K2 Wc

Wc = being the metallurgical depth of the collector. K2 being equal to  $\approx 10 V/\mu m$  for an NPN transistor.

We also have:

G = HFE IC=K1 AE/Wc<sup>2</sup> AE being the emitter area ie

$$G = \frac{K3}{(VCEO sus)^2}$$

An more precise analysis gives us:  $G = \frac{K3}{(VCE sus)^2}$ .3

which is very restricting, because in order to increase VCEOsus significantly while maintaining high current gain requires a substantial increase in chip area.

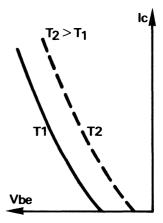

#### A-4.4. TEMPERATURE VARIATION

The breakdown voltage of a planar junction increases with temperature because the level of recombination increases as the square of IL, at the same time the level of generation increases linearly with temperature and the electric field increases, thereby restricting the number of collision.

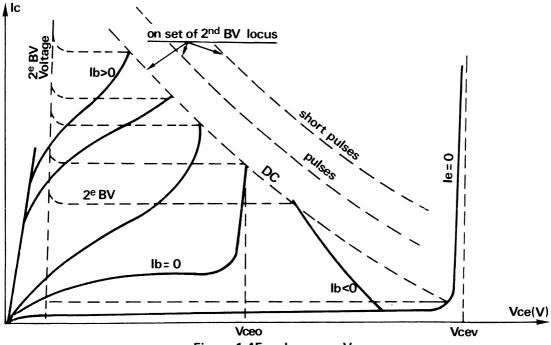

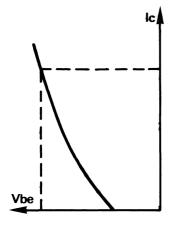

#### A-5. Second breakdown - 2nd BV under forward biased conditions

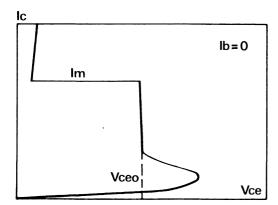

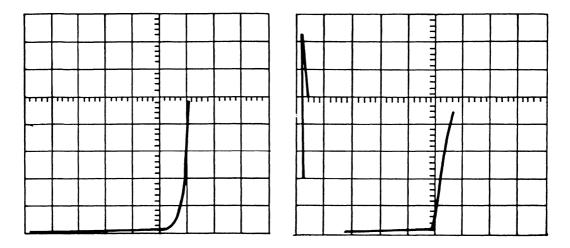

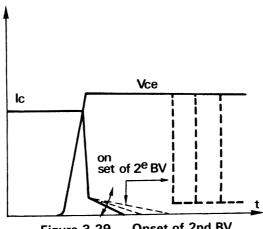

Physical phenomenon: if a power transistor is driven into avalanche (ib = 0) and allower, to reach Im current, a sudden collapse of voltages will be observered and the current through the transistor will be limited only the external circuit. This phenomenon is called, second breackdown and is represented graphically in Figure 1-32.

Figure 1-32 - Second Breakdown

Figure 1-33 — Current density under the emitter finger

This phenomenon was first described in 1958. Later it was discovered that it was not necessary to pass through the first avalanche to have a second breakdown and that it could come about through forward biasing of the base.

The lm current decreases as collector voltage increases by observing this phenomenon with short power pulses it can be seen that the material is temperature depend.

The lm  $\times$  Vce product is always less than the Pmax of the device. This phenomenon is a basic property of semiconductors. In 1966, using an N+N N+ structure (i.e. a slice of so-called intrinsic silicon between 2 slightly resistive ohmic contacts), Japanese researchers caused the same phenomenon to appear when a critical voltage current point was reached.

The temperature of the crystal at this moment was between 200 and 300°C inclusive for the resistivities of the materials used (temperature inversely proportionate to resistivity). This temperature corrresponded with that of the intrinsic conduction of the semiconductor (that is to say, at the moment when it becomes identical to a conductor). It was also noted that the phenomenon of intrinsic conduction does not immediately distroy the materials.

Today, we know that at least two phenomena are responsible for the second breakdown in power transistors.

#### A-5.1. A THERMAL PHENOMENON

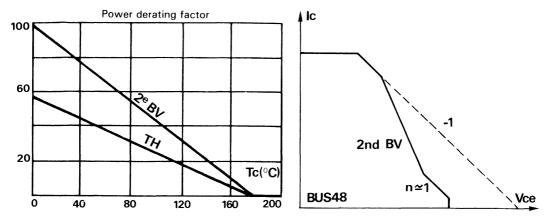

When a transistor is forward biased, a transverse electric field appears in its active base region, because of bulk resistance, this field tends to grownd current towards the edges of the emitter fingers: Figure 1-33.

Since the current density increases significantly at the edges of the emitter fingers overheating may occur locally with the appearance of "hot spots". These in turn created low resistive paths for the current and the current density to increase further resulting in thermal instability as studied by Scarlett and Schokley in 1963.

Depending on the voltage and current levels, this phenomenon can be degenerative to the point of the 2nd BV and the destruction of the transistor by punch through on the edges of the emitter fingers.

But it can also be relatively stable and not reached second BV, this will appear as instability of the breakdown waveform on a scope or curve tracer.

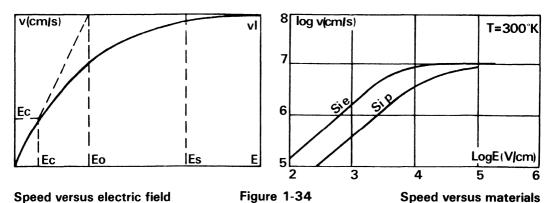

We said previously that carrier speed is  $v = \mu o \epsilon$  this is only true in reality for weak electric fields, when the electric field is increased A value of  $\epsilon_C$  fields is reached, after

which, speed does not increase and:  $v = \mu o \sqrt{\epsilon \epsilon_C}$  continued increase in field strength will produce a saturation point,  $\epsilon_S$ , at this point the speed is constant which

gives:  $v = \mu o \sqrt{\epsilon_C \epsilon_S}$  This relationship is shown graphically in Figure 1-34.

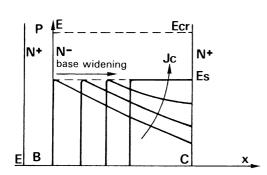

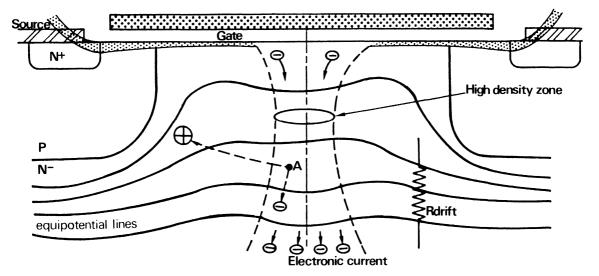

If we again look at the high voltage power transistor in Figure 1-23, and the  $\epsilon = F(x)$

relationship we get the following Figure 1-35.

For a constant VCB voltage(area below the curve is constant) and an electric field less than Es, the current is small at first, the field slope as a function of x is identical to Figure 1-24.

When the current is increased, Jc increases, electron speed must increase and for this to happen, the field must increase. This can only be done by displacing the curve as shown in Figure 1-35. Since a function can be characterised by the fact that dE/dx is infinite, we see that a displacement of the metallurgic collector base junction in the low doped zone of the collector, effectively widens the base (Kirk effect 1962). A limit is reached when the field is at saturation Es, additionaly Jc/V = qNc and dE/dx = 0 (flat curve). At this point carrier speed cannot increase, which means that excess carriers must be injected into the N- region. These injected carriers are supplied by the emitter, giving a negative value for dE/dx and a linear relationship of E=kx.

Figure 1-35 — Field versus distance

Figure 1-36 — Base widening

For each increase in I there is an increase in Jc this widening of the base and steepening of the slope continues until the field at interface N-N+ reaches the critical field value Ec, Figure 1-36.

At this moment, the avalanche occurs, a large quantity of electron hole pairs are created, electrons move toward the collector (NPN) and the holes, toward the base: there is an injection of holes due to the avalanche thus the term avalanche injection and the possibility of negative resistance and destruction.

The important phenomenon here is the effect of base widening, resulting in a decrease in transistor gain. If the base current is constant, the local current density decreases and hot spots are reduced, resulting in a stabilisation effect. This effect could not exist in single diffusion transistors.

P.L. Hower, in 1973 gave a formula for stability factor S:  $S = RTH \ VCE \ \delta Ic / \delta T$  (8) If S < 1, the inhomogeneities of junction temperature decrease with overall temperature and the product becomes stable.

If S>1, as soon as a hot spot appears, the system tends to degenerate with time (1 ms and over).

Suppose that the 2nd BV survives when S = 1, the power dissipation in the device is:

$$P_{SB} = Ic V_{Ce} = \frac{1}{RTH} \frac{Ic}{\delta_{Ic} I \delta_{T}}$$

(9)

We see immediately that if we want to increase PSB, we must decrease RTH i.e. increase the size of the chips assuming that current density stay constant.

We can predict the stability point by the formula:

$$Vce INTH = \frac{lc Re + Tc \cdot k/q \cdot Ln (I1/IC)}{k/q \cdot (Ln I1/IC - 1) \cdot lc R\theta jC} - \frac{Tc}{lc R\theta jC}$$

(10)

Vce INTH: collector - emitter voltage at a given Ic for which thermal stability exists.

Ic = collector current

RE = emitter series resistance

Tc = case temperature (°K)

It is defined by the following equation:

$$I1 = Ic \exp \frac{-q \text{ (VBEJ-Eg)}}{KTj} = \frac{qAE \text{ nio}^2}{QB|DB}$$

(11)

VEBi = internal base emitter voltage

VEBi = internal base emitter voltage

$E_Q =$  forbiden band ( $S_I = 1.1eV$ )

$T_i = \text{junction temperature } (\circ K)$

AE = emitter area

Nio =  $2.46 \cdot 10^{19} \text{ cm} - 3$  for the silicon

QB = the number of majority carriers in the base per unit of area

DB = the coefficient of diffusion of minority carriers in the base

QB/DB = is often called GUMMEL number

All these physical values can be measured or calculated.

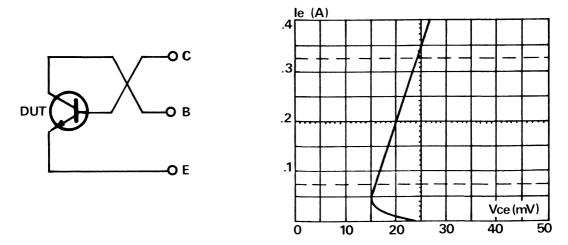

RE (emitter resistance) can be measured on a curve tracer connecting the base to the collector terminal, emitter to ground and leaving the collector open.

The waveform on the curve tracer is shown in Figure 1-37.

Figure 1-37 - Emitter resistance measurement

The value of RE is the slope (VE/IE) of this curve at the higher current levels.

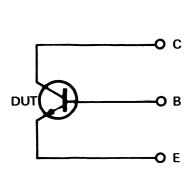

For this example RE = 33 m $\Omega$  to calculate I1, we can also use a curve tracer to find VBEJ. For this measurement the device is mounted normally in the test jig, the measurement is taken at low IE, so that results are not distorted by the presence of RE, and assume IE = Ic on the horizontal axis set value of VBE on the screen (Figure 1-38).

Figure 1-38 - VBEJ measurement

For this example IE =  $100\mu A$ , VBEJ = 460mV and we calculate I1 =

$$10^{-4} \exp \frac{-1.6 \cdot 10^{-19} \cdot (.46-1.1)}{1.38 \cdot 10^{-23} \cdot 300}$$

$10^{-4} \exp \frac{10250}{414} = 10^{-4} \exp 24.8 = 10^{-4} \cdot 10^{10}.7 = 10^{6.7} = 510^{6} A.$

If we wish to calculate Vce INTH for IC = 0.5 and ROJC = 1°C/W, we have: Vce INTH =

$$\frac{0.5 \times 3 \times 10^{-2} + 300 \times 863 \cdot 10^{-7} \text{ Ln } 10^{7}}{863 \cdot 10^{-7} (\text{Ln } 10^{7} - 1) \times 0.5 \times 1} - \frac{300}{0.5} = 40 \text{V} \text{ so Vce INTH} = 80 \text{V if } \text{ReJC} = 0.8 \text{ °C/W}$$

In actual use of power transistors it is not advisable to enter this region, even if there is no degenerative phenomenon.

In fact, prolonged use with hot spots at a temperatures of 200 to 300°C automatically causes parasitic diffusion or long term dislocation, resulting in a significant reduction in reliability.

#### A-5.1.1. How to detect the development of hot spots?

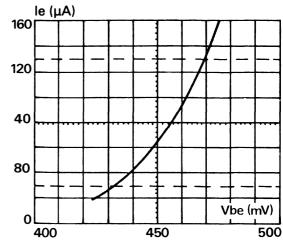

It is well known that VBE voltage in silicon transistor decreases at about 2 mV/°C.

When hot spots develope the temperature increases suddently and so VBE decreases suddenly.

By observing the changes in VBE as the load (VCE $\times$ IC) increases, one can detect the appearance of hot spots (Figure 1-39).

A-5.1.2. What are the technological changes that can be made to the power transistor to improve its performance at second breakdown?

If we take stability factor S (equation 8), we can rewrite it as follows:

$$S = \frac{(T-TA)}{T} \cdot \frac{(kT/q \ln (fI/lc) + (kRB/HFE) \Delta E/kT}{kT/q + lc (RE + RB/HFE)}$$

assuming the device is controlled by a voltage source.  $\Delta E$  "activation energy" is approximately 0.15 eV for a triple diffused transistor, 0.05 eV for a planar, and 0.1 eV for a double diffused, kT/q = 26 mV to 300°K.

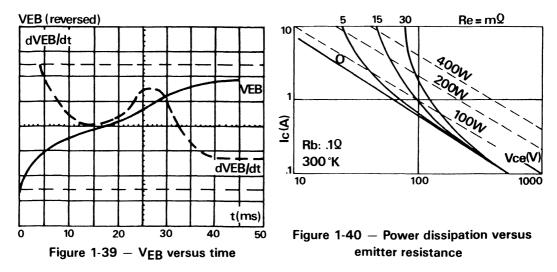

According to formula 12, we see that if we increase internal RE resistance, the stability factor S decreases, if we set S=1: limit for thermal stability, the level of 2nd BV (PSB – ESB) increases linearly with RE if Ic is held constant. If VCE is held constant, we can say that PSB rises exponentially with RE (Figure 1-40).

These RE effect only occur at high currents. We say, from equation 9, that we can improve PSB reducing RTH.

Since S is dependent on RE it is also dependent on RB, however its effects are less because of the HFE of the transistor, but are dependent of the variations of HFE verses temperature.

If the HFE increases with temperature, RB contributions is reduced.

If the HFE is independent of temperature, we increase the contribution due to RB.

We can say that, appart from the fact that HFE = f(Ic) in the region where Ic is decreasing: HFE(T) = constant .exp ( $-\Delta E/kT$ ) thus the fechnologies which tend to increase  $\Delta E$  are more sensitive to the presence of RB. (See as an example the following 2 graphs 1-41 and 1-42):

Figure 1-41 and 1-42 — Power dissipation versus base resistance

In spite of its reduced affects, RB has the advantage of not affecting the VCEsat and therefore losses, nor the gain, nor the switching times.

#### A-5.2. THE AVALANCHE INJECTION

This model is appropriate when high current densities and strong electric fields are simultaneously present in the low-dope N- region of the collector of a high voltage power transistor.

At high supply voltage, the depletion region is very large and the concentration of current is considerable. This means that even if the value is low, current density on the edge of the emitter finger can be very large (see Figure 1-33).

If we take the model of Figure 22 again, and graph  $\epsilon = f(x)$  with high VCE = constant we obtain Figure 1-43.

thermal instability limit

Limit of 2<sup>e</sup> BV

Log Vce

Figure 1-43 — Collector field

Figure 1-44 - 2nd BV limits

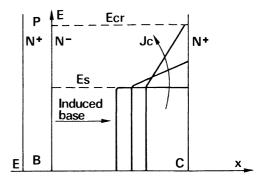

Given a high voltage, leads us to assume that speed is at saturation level, and Poissons's equation applies:  $\frac{d\epsilon}{dx} = \frac{1}{\epsilon} \left( qNc - \frac{Jc}{v} \right)$

We can simplify the solution by the looking at what happens when Ic is increased, Jc is increased by electrons injected from the emitter,  $v = v_S$  is constant, and there is a decrease of d  $\epsilon/dx$  as Jc increases up to d  $\epsilon/dx = 0$  (horizontal line) when  $J_C/v = qN_C$ .

The maximum field moves away from the critical Ecr field, the breakdown can now take place at higher voltage.

When Jc = qv Nc is passed, the excess electrons compensate the space charge in the depleted N- region and force the curve to reverse.

It becomes negative until the critical field is attained at the interface N-N++ and we get breakdown injection: see thermal phenomenon at the limit of the second breakdown, previous paragraph.

Here there is little or no base widening effect, so there are no stable hot spots in the thermal instability region and we immediately move into the secondary BV (see curve 1-44, below value I\*).

The secondary breakdown limit is found approximately on a hyperbole represented by:

$$ISB = \frac{k}{VCE^{\Pi}}$$

(13)

n being between 1.5 and 4 depending on the types of transistor and junction (gradual or abrupt).

This is always less than the maximum thermal limit given by the manufacturers because in this region only 8 to 10% of the silicon is used for conduction.

Moreover, the stability factor in this region is S=1 and gives us a mean junction to case temperature as follows:

$$\Delta T_{jb} = \frac{TA}{Ln (11/|C) - 1}$$

(14) If we take I1 found previously on page 1-28, I1 = 510<sup>6</sup>A TA = 300°K for IC = 100 mA, we get:  $\Delta T_{jb} = \frac{300}{Ln (510^{7}) - 1} = 18$ °C

Because of the logarithmic form of formula 14, one could say that the difference of junction to case temperature in second breakdown state is relatively constant, between 16 and 18 °C, which is substantially different than the temperature differences given by manufacturers.

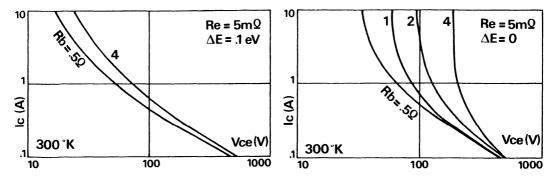

Figure 1-45 — Ic versus Vce

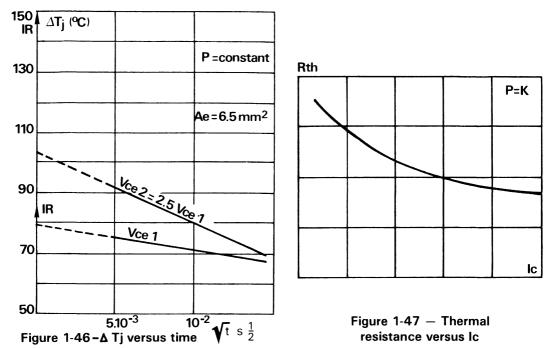

### A-6. Thermal resistance at high voltages

The previous paragraph leads us to consider that a products thermal resistance is much higher than indicated by the manufacturers when device is subjected to high voltages. This phenomenon can be proven by appling the same power pulse to a device but at different potentials, and measuring the junctions temperature by on of two different methods:

- variation of VBE = F(T)

- with infrared radiometer

We have already seen in the "thermal resistance" section, that for short times, the unidimentional heat flow may be used according to the following relationship:

$$T(t) - T(0) = K\sqrt{t}$$

(15) which is represented graphically in Figure 1-46.

The infrared (IR) measurements have also been marked on this curve.

Two statements can be derived from this:

- when voltage increases, junction temperature increases significantly (VCE 2 = 2.5 VCE 1).

- The conventional measurements reduces the junction temperature even more as the voltage rises because this measurements tends to spread out the temperature (medium temperature) error of -4 °C at VCE = 40 V, error of -50 °C at VCE = 100 V.

The conclusion which users of power products can draw from this phenomenon is that they should be especially careful when using these products at high voltage since this involves 2 potential risks:

- the risk of degradation from non-destructive hot spots.

- the risk of not having a sufficient safety margin under actual circuit conditions because of the reduction of the useable area of the chip.

The apparent variation of thermal resistance can be shown here, as a function of constant power current (i.e. in function of I/V), Figure 1–47.

#### A-7. Pulsed FBSOA

#### A-7.1. THERMAL LIMITS

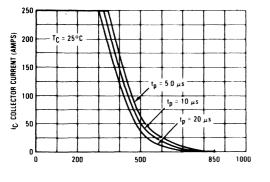

A maximum ICM value is generally set equal to twice continuous IC for a portion of curves given by the manufacturers  $\delta \le 10\%$ .

For the Pmax rating a constant value with a slope of -1 on logaritmic coordinates is used. The value of Pmax is calculated from the transient thermal impedance curves and  $\delta \leq 10\%$  (see thermal resistance).

#### A-7.2. LIMITS CREATED BY ELECTRIC FIELDS

Typically BVCEO is consider to be independent of temperature.

For the secondary breakdown (hyperbola ISB=kvce-n) the limit is considered to decrease linearly with the tenperature, and usually at a slower rate than Pmax because "hot spots" are affected more by the electric field than by temperature.

Figure 1-48: FBSOA curve

Figure 1-49 — Low voltage transistor FBSOA

When working under impulsed conditions the following methods are used analyze performance type of devices.

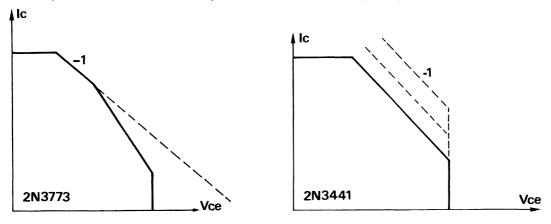

A-7.2.1. For low voltage device the dissipation limit is typically less than the ISB, there is no problem here, its the first limit that counts. Low voltage transistor, "Power Base" type 2N3441.

A-7.2.2. For high voltage double-diffused devices the limit for the secondary breakdown is always less than the dissipation limit, it is clearly the second BV limit which counts. High voltage transistor, double diffused type: BUT15.

Figure 1-50 — Double diffused transistor FBSOA

A-7.2.3. In general for medium-voltage (100-500 V) power transistors, such as the 2N3773, exhibit all four SOA characteristics and are derated with temperature as shown in Figure 1-51.

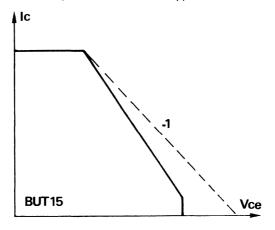

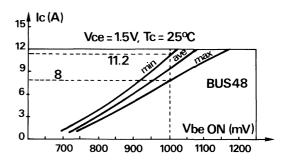

A-7.2.4. In the special case for very high voltage triple diffused transistors such as the BUS48, secondary breakdown is the predominate segment as shown in Figure 1-52.

Figure 1-51 — Power derating factor

Figure 1-52 — Triple diffused tansistor FBSOA

We now see the appearance of a additional break in the 2nd BV curve for high voltages and there is a new resistance type slope with  $n \cong 1$ , this being attributed to widening of the base in the low-resistive N- region of the collector.

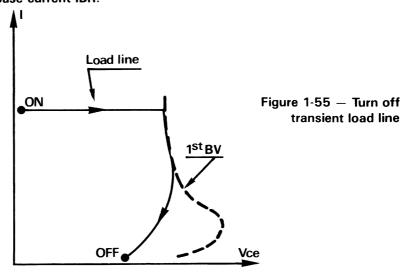

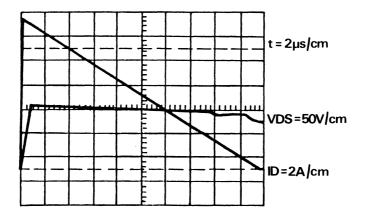

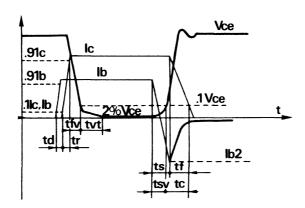

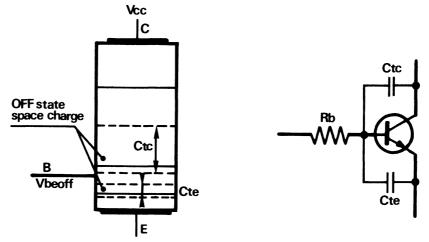

# B) Switching safe operating areas

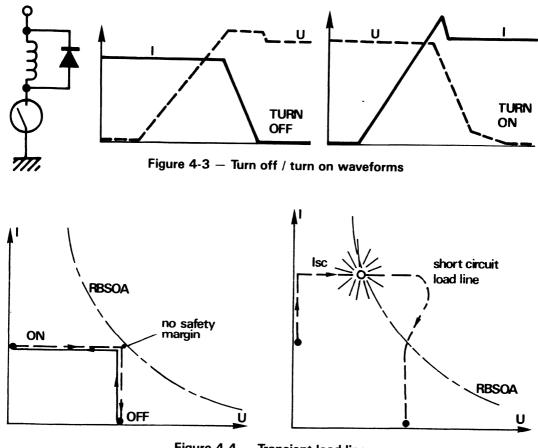

#### B-1. At turn off

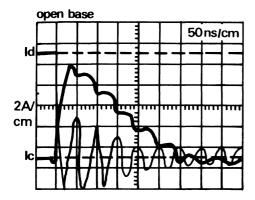

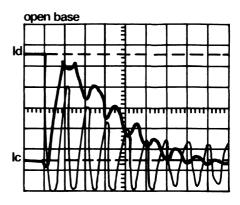

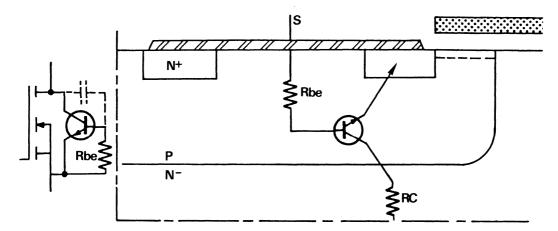

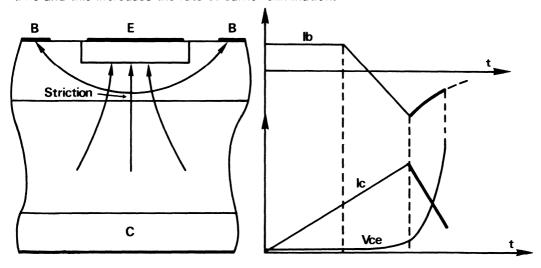

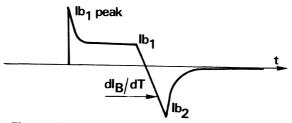

We discussed at the end of the previous chapter the sensitivity of second breakdown at high voltages and low load currents. If this condition is maintened for negative-based currents, the phenomenon of second breakdown without the preliminary appearance of thermal instabilities always occurs. The destruction of the component is very fast, once the phenomenon occurs, probably less than a few hundred nanoseconds. However, if this behavior is analyzed closely the results shown that the mechanism is not quite identical.

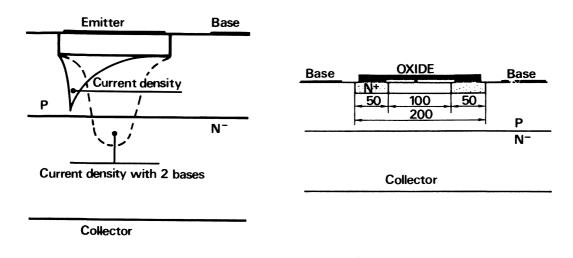

Now, the electric field in the base is reversed, base current flowing through the internal base-emitter junction is forced through the center of the emitter fingers because of the edges being turned off harder than the center (see Figure 1-53). The higher the base-emitter reverse bias the higher the current density in the center.

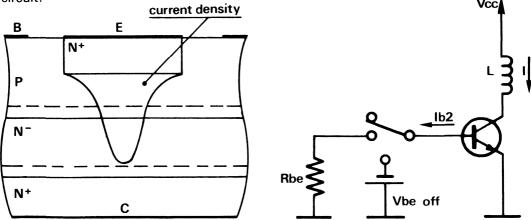

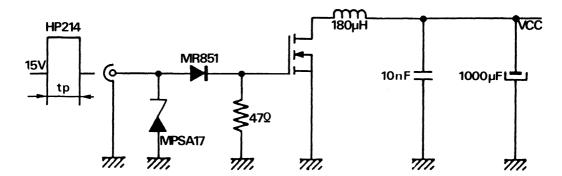

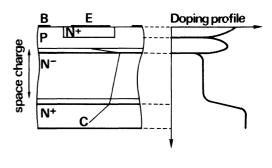

One of the classic case on stressing power transistors during turn off is in an inductive circuit.

Figure 1-53 — Turn off current density

Figure 1-54 — Test circuit

In this circuit the current does not want to change instantly so the potential at the transistor VCE terminals increases rapidly approaching BVCES until the energy stored in the inductance is dissipated:  $E = 1/2 \text{ LI}^2$ .

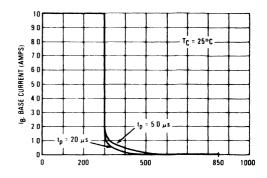

In reference to the transistor capabilities, E becomes ESB (Energy Second Breakdown) and I becomes ISB (Intensity of Second Breakdown) for the specified values of **inductance L and reverse base current IBR**.

When IBR is higher than a certain value which gives an intersecting voltage which is greater than kT/q we can say the intensity of the second breakdown (9) is:

$$ISB_{min} = \frac{2Z^2J_T kT/q}{RS IBR}$$

(16)  $Z = being the emitter perimeter RS = base resistance$

$J_t$  = critical density of current corresponding to the limit of the avalanche injection (see chapter A-5.2)

$J_t = q_V eND$ , Ve being the speed limit of electrons in the silicon:  $10^7$  cm/s

From this equation we deduce immediately that the intensity of the secondary avalanche is proportional to the square of the emitter perimeter and inversely proportional to the base resistance and reverse base current (IBR).

We shall now look at the relative influence of these different parameters on the intensity of the secondary avalanche.

Let us take the case of an inductive load being turned off.

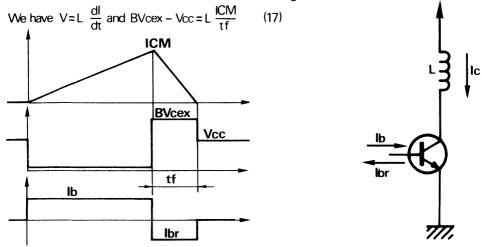

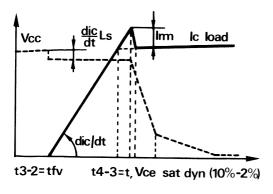

Figure 1-56 — Turn off on inductive load

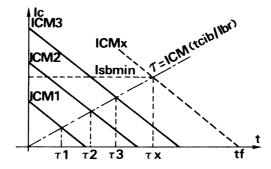

Which can also be written up: IC(t) = ICM (1 - t/tf).

# **B-1.1. ELECTRONIC MODEL**

Supposing that L is sufficiently great to have bigger tf than the natural tf of a power component otherwise BVcex would not be attained.

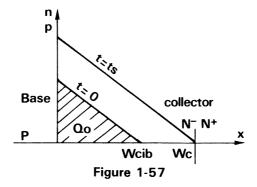

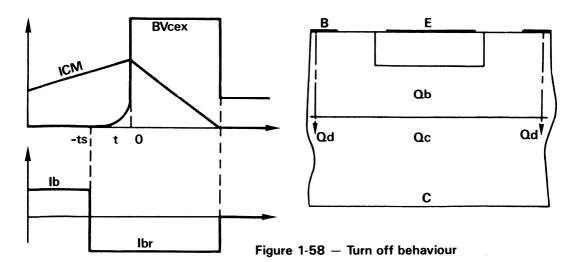

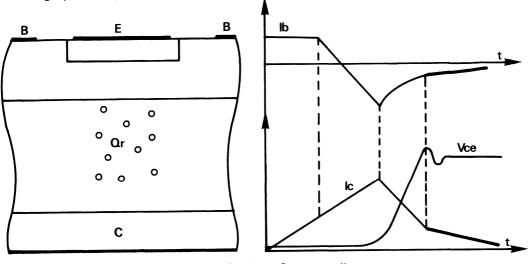

If a high voltage device with low doping of N- collector is in the on state, there is an excess of minority carriers in this N- region.

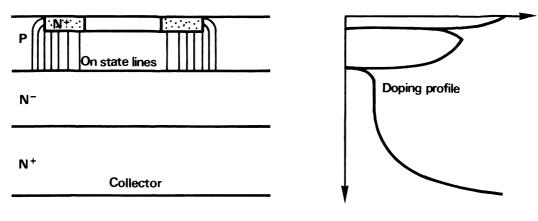

At the beginning of turn off these charges are reduced, the excess holes are removed from the base and excess electrons from the collector. Tests show that an excess of holes exists in the collector when operating at saturation (up to junction N-N) and that they must be removed before any change (Qd), occurs outside in the load circuit.

Figure 1-58, between time -ts and time = 0, the base current extracts Qc and Qb charges, which is part pf the amplification phenomena, VCE voltage begins to rise and the constriction of current begins to take place at the center of the emitter finger.

At time t = 0 where the collector voltage reaches BVcex, there still is a specifics quantity of charge Q (0) in the collector. One can say IBR = dQ(0)/dt.

After a specific time  $\tau$  , there is no longer any stored charge and the load current begins to decrease.

$\tau = Q(o)/IBR$  (18) This can also be written as ICM = Q(o)/ $t_{cib}$  (19) with  $t_{cib} = 4 \frac{W^2 cib}{DC}$  DC being the diffusion coefficient of minority carriers in the collector.

The charge Q(t) excess is important because it reduces the value of base resistance RS (eq 16) during fall time  $0 \le t \le tf$ , Q and IC decrease linearly with time the condition  $\tau \le tf$  implies that Q reaches zero before the load current.

In this case, a second breakdown may arise if  $Ic(\tau)>ISBmin$ , when a component is tested for second breakdown energy, the IBR is fixed and ICM is increased just until this phenomenon is produced for a reverse base current fixed at IBR, charge recovery time is:  $\tau = ICM$  (tcib/IBR) (20)

The equations 18 and 19 come from the slope line ticb/IBR in the plane ICM = F(t). Therefore the collector current IC ( $\tau$ ) values for which the constriction arises are located in the mixed line on this graph.

Figure 1-59 — Maximum current versus time

ISB min is obtained from equation 16 can be shown also we can see that collector currents ICM1 < ICM2 < ICM3 do not lead to the secondary avalanche as IC( $\tau$ 1) < IC( $\tau$ 2) < IC( $\tau$ 3) < ISB min.

The secondary breakdown will arise for an ICM(x) current value which will give a value IC(x) = ISBmin for maximum constriction.

But when testing the device the value of the intensity of secondary breakdown is ICM(x) therefore we can write:

ICM (x) = ISBmin/

$$\left(1 - \frac{\tau x}{tf}\right)$$

and ISBmin = ISB  $\left(1 - \frac{t}{tf}\right)$ , from the equation 17

we have tf = ICM/(BVcex-Vcc), from the equation 20,  $t = \tau = ICM$  (tcib/IBR) so ISB =  $\frac{ISBmin}{1-L_1/L}$  (21) if we say that  $L_1 = \frac{tcib (BVcex-Vce)}{IBR}$

This equation indicates that the intensity of the secondary breakdown increases as load inductance decreases to value L1 = L where it is theoritically infinite.

Values of inductance L less than L1 imply that  $\tau$  is greater than tf, which shows that pinching does not occur during current fall tf; and RS remains modulated by conductivity.

One can say that at this point, the secondary breakdown does not occur because of avalanche injection, but because of thermal effects which we shall now study.

#### **B-1.2. THERMAL MODEL**

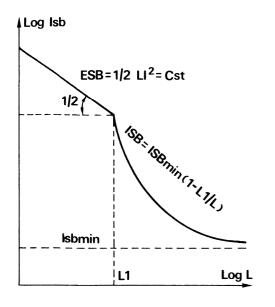

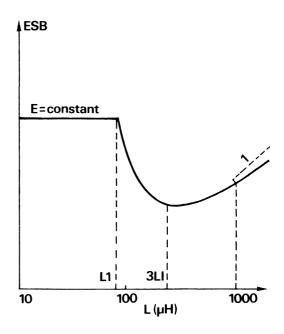

If we assume that all the energy stored in the inductance changes into heat in the transistor and causes the temperature of the active region of the power transistor to increase diabatically, then for an identical temperature, we get a secondary breakdown

constant energy of:  $ESB = \frac{1}{2}L ISB^2$  in the ISB = F(L) graph we have:  $ISB = k L^{-1/2}$  thus a

- 1/2 slope line on logarithmic co-ordinates.

# **B-1.3. GENERALIZATION OF MODEL**

The model will have a particular point L = L1 defined by the physical parameters of the power component and base control.

B-1.3.1. If L<L1 it is possible to have a second breakdown by thermal effects for a constant energy.

B-1.3.2. If L>L1, second breakdown by injection on the ISB=F(L) graph, gives:

ISB =

$$\frac{|Smin|}{1-L1/2}$$

i.e. a hyperbole, Figure 1-60, approaching ISB = ISB min

If we make curve E = F(L) we get Figure 1-61.

the first part up to L=L1, we have E=constant, then by making L=kL1, we obtain:

$$E = \frac{1 + k^3}{2(k-1)^2} L_1$$

ISBmin which has minimum a value for  $k = 3$  and infinite for  $K = 1$ , for

K = 10, if we assume a 10% error, we get E = kL1 ISBmin.

Figure 1-60 — ISB versus inductance

Figure 1-61 — ESB versus inductance

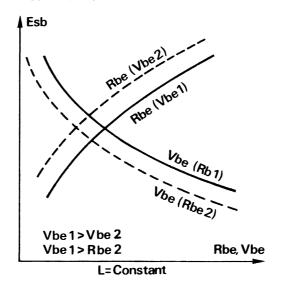

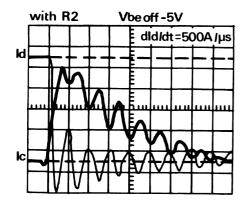

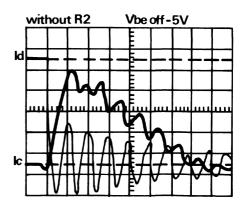

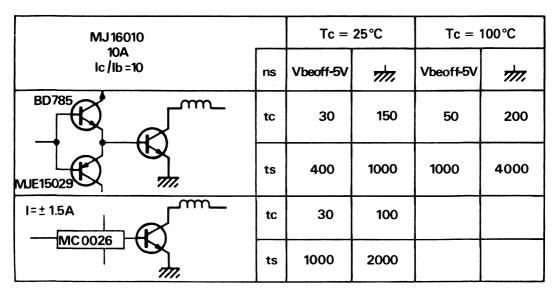

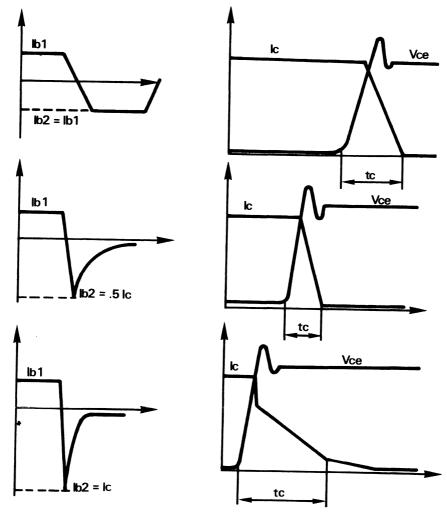

B-1.4. Charges in secondary breakdown verses RBE and VBE (off) we have seen ESB = F(L), we must now look at ESB = F(VBE, RBE).

The ISB formula (16) indicates that ISB varies inversely with IBR. At RBE = constant, if VBE (off) increases IBR rises then ISB and ESB decrease.

Figure 1-62 - ESB versus Rbe, Vbe

In the same way, at constant VBE, if RBE increases, IBR decreases and ESB increases. All of this at constant inductance L (Figure 1-62).

### B-1.5. CRITIQUE OF MEASURING THIS PARAMETER

Even if we measure the energy of the secondary breakdown for a power transistor with a non-destructive circuit, it seems clear that this attempt endangers its reliability. It is also clear that the maximum energy the transistor can support before secondary breakdown is very sensitive to the value of the circuit inductance.

Finally, the energy capability decreases when IBR is increased, however IBR is typically increased to improve switching times and thus reduce losses in the power transistor. Reducing the temperature improves long term reliability.

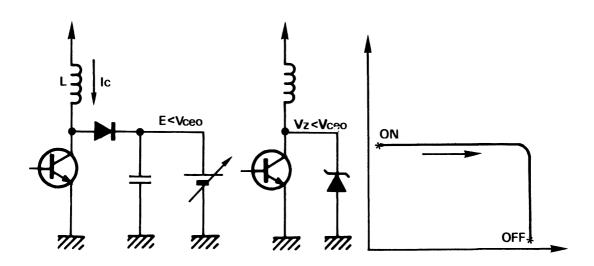

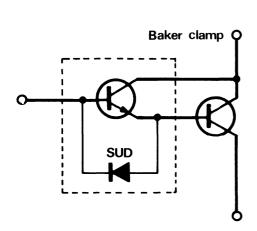

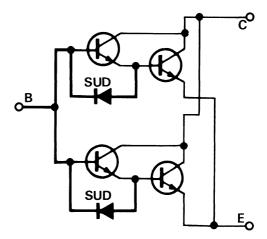

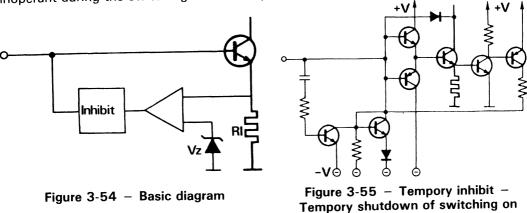

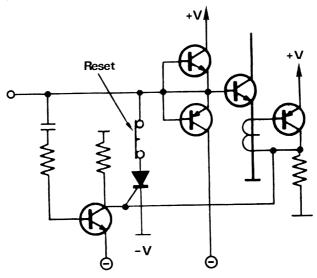

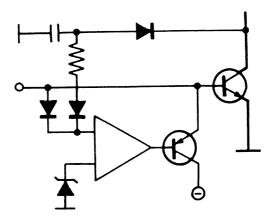

It would seem that the best approach is not to drive the transistor into secondary breakdown to prevent this the power transistors must be protected either by a zener or by a protection circuit (see following chapter).

The performance of the power switch is voltage-protected or clamped is different than the performance we have just looked at and will be described in the following paragraph.

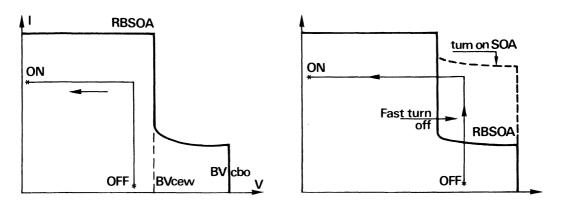

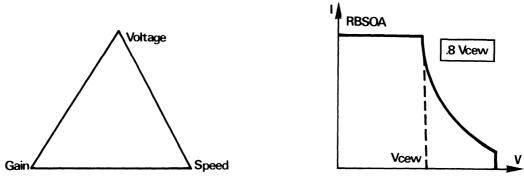

#### B-1.5.1. Reverse bias safety operation area (RBSOA)

The test is performed by using the circuit shown in Figure 1-63.

Figure 1-63 — RBSOA test circuit

Which represents a more typical application than the unclamped inductive switching circuit. This circuit can be designed to be non-destructive and to have no effect on the long term reliability of the device being tested.

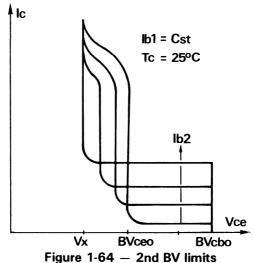

The points where the secondary breakdown begins are shown in Figure 1-64.

The relationship is shown for different values of reverse base current IBR = IB2 there are two main sections for these curves.

B-1.5.2. A vertical section, varying very little with IBR. We have an avalanche injection phenomenon here: high current density (100 to  $1000 \, \text{A/cm}^2$ ) and strong electric field (VCE $\cong$ VCEOSUS), the critical field moves to toward the N-N+ junction (see paragraph A-5.2). The instable area tends to reduce itself to a small spot at high temperature (500 to  $600\,^{\circ}$ C) at the center of the emitter finger and quickly destroys the device.

Figure 1-65 - RBSOA versus To, Bf

B-1.5.3. A more or less horizontal section at lower currents. At this point most of the avalanche injection current is removed by means of the reverse base drive. If this removal is large enough the secondary breakdown capability will be increased even at righer voltages.

The second beakdown mechanism can be explained in this region by the increased conduction of small transistors near the center the emitter finger at the moment of turn off. Which is a result of high base current and internal base resistance.

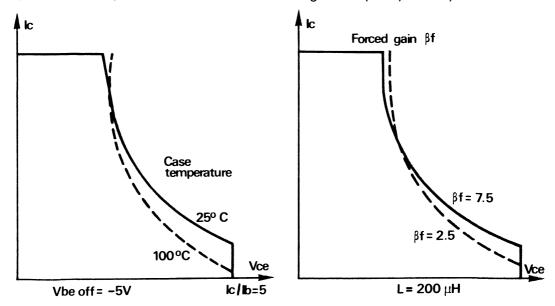

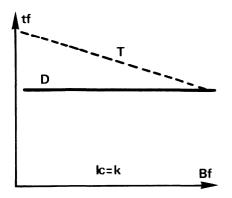

In Figure 1-65, the changes in RBSOA capability are shown as a function of temperature and forced gain we note on the first curve that RBSOA decreases predominately at low currents when the junction temperature increases.

On the second curve, we see a similar characteristic, the RBSOA decreases at low currents when the transistor is highly saturated before turn off ( $\beta F = 2.5$ ).

The accumulation of carriers under the center of the emitter fingers explains this variation.

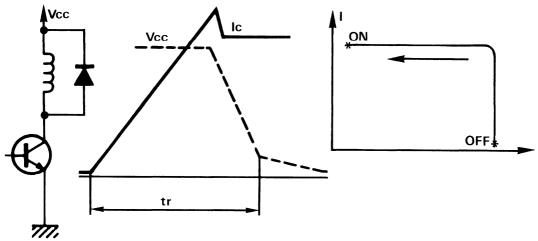

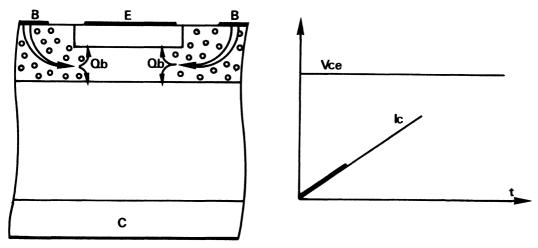

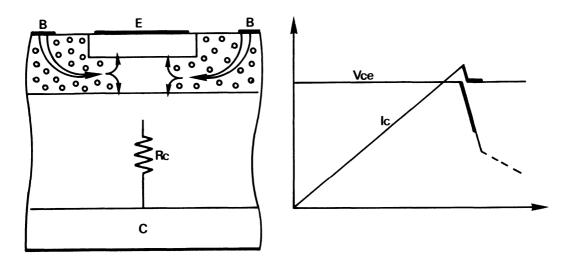

#### B-2. Safe operating area at turn on

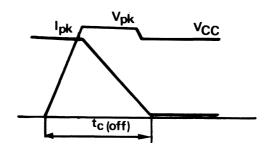

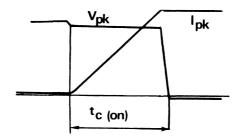

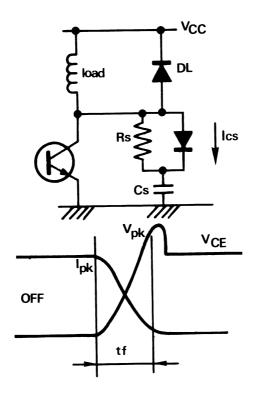

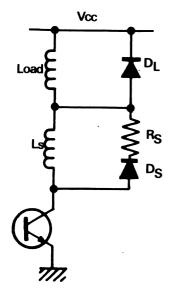

In most inductive circuits, the current and voltage waveforms during turn-on are similar to those shown in Figure 1-66.

Figure 1-66 — Turn on in inverter leg

The turn-on load line appears to be identical to the turn-off load line, but the devices has much more capability in terms of secondary breakdown for the forward biased condition that it does for the reversed biased condition. This is due to the fact that during turn-off the current is forced into a small area at the center of the emitter, as oppose to turn-on where the current is forced to the edges of the emitter fingers and the same current density is spread out over a larger area.

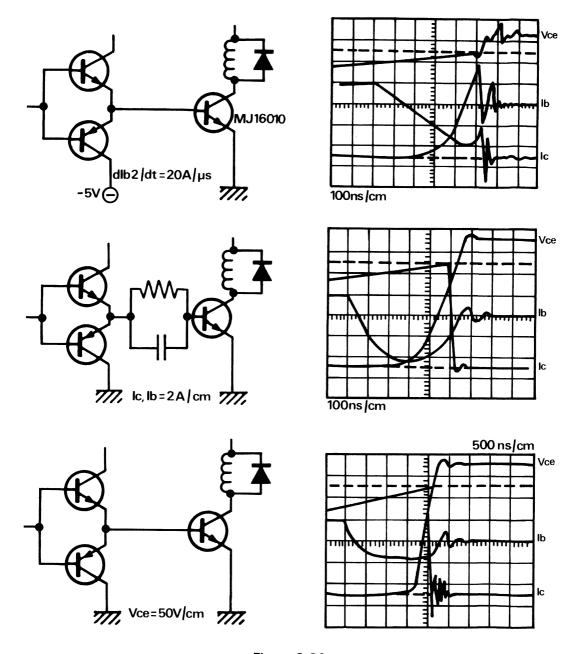

If we use a controlled base drive at turn on: Ibl at turn on equal to 3lbl at turn off and a dlbl/dt as large as possible, we avoid excess heating since the turn on losses are proportional to turn on time  $t_r$  and the secondary breakdown region is traversed quickly (vertical part of safe operating: less than 100 nanoseconds).

This result in a lower probability of destruction due to secondary breakdown. Finally the off condition is determined by the value of supply voltage, which should be lower than the BVceo of the transistor. The load line should lie within the boundaries of the RBSOA curve as shown in Figure 1-67.

The BVcew is typically set at BVceo for discrete and darlington, however, the BVceo rating of a darlington typically includes internal resistors and is in reality a BVcer rating. For turn on with a supply voltage higher than BVcew, the boundary of current at a specific BVceo can be increased by factor 4 or 5 if this region is traversed quickly, typically less than 100 nanoseconds. Recent test indicate that this can be done with any degradation to the device.

Figure 1-67 - Turn on load lines

Figure 1-68

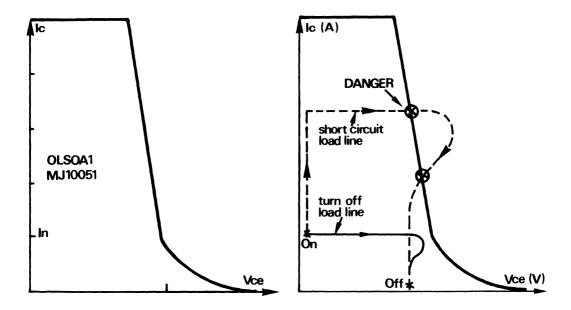

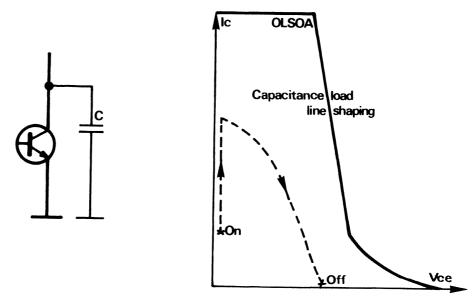

# C) Overload safe operating areas

(OLSOA: overload safe operating area).

There are two typical applications where overload currents may exist (maximum overload).

The external circuit fixes the lc current in the collector: this is the most common case (i.e. inductive circuits).

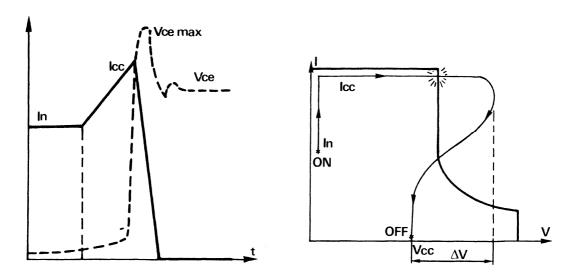

The circuit has zero or low resistive inductance (dlc/dt may be infinite) in this situation the transistor gain fixes the short circuit current.  $lcc = \beta l_B$  for the power switch itself two conditions may exist: when a temporary overload current occurs, the device remains in saturations. In this case, the transistor is very strong and can sustain many times its maximum current rating may which reach 5 times I nominal.

General case: the overload is permanent: when the device senses condition, it begins

the power circuit may be opened by saturation and can reach:  $Vce = Vsupply + LS \frac{dlcc}{dt}$

LS being the parasitic inductance due to wiring.

The LS dlcc/dt value may be very high because the device takes a certain amount of time to react and the transistor has a non-negligeable storage time, which means the Ice may be high or equal to 2I nominal, turn off time tf = dt is very fast which results in the device pulling out of saturation and Vce rising very rapidly as shown in Figure 1-69.

Figure 1-69 — Short circuit transient load line

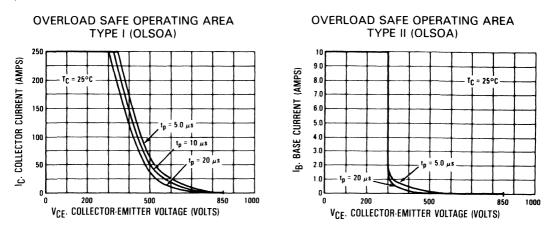

Refering to Figure 1-70 the overload safety areas will be of two types:

#### C-1-. OLSOA I

Is measured in a common base circuit which allows precise definition of collectoremitter voltage and collector current.

#### C-2. OLSOA II

Applies when maximum collector current is not limited by circuit design, but is limited only by the gain of the transistor.

V<sub>CE</sub>, COLLECTOR-EMITTER VOLTAGE (VOLTS)

VCF, COLLECTOR-EMITTER VOLTAGE (VOLTS)

Figure 1-70-Overload safe operating area type I and II (OLSOA)

### C-3. Bibliography

- (1) Greg OWEN, Thermal management techniques keep semiconductors cool. (Electronics, Sept. 25, 1980)

- W.E. NEWELL, "Transient thermal analysis of solid state power devices making a dreaded process easy"

(IEEE Power Electronics Specialists, 1975)

- (3) GENERAL ELECTRIC, SCR Manual, 1979

- (4) AN569 MOTOROLA, "Transient thermal resistance general data and its use", 1972

- (5) A. FILLATRE, "Comparaison des performances limites à l'état passant des transistors de puissance bipolaires et MOS"

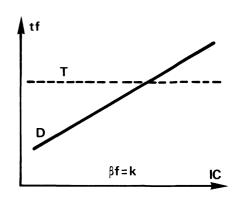

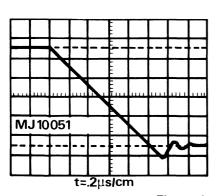

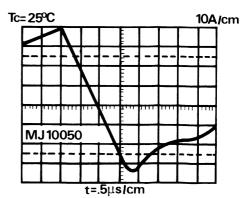

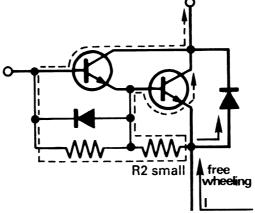

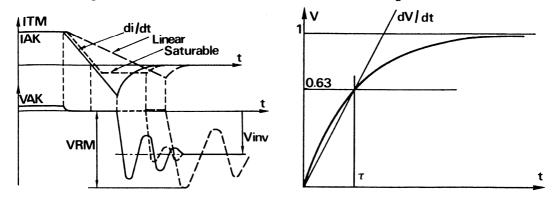

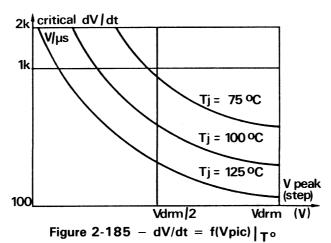

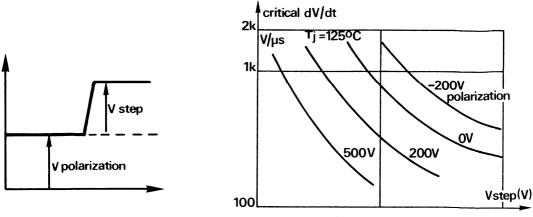

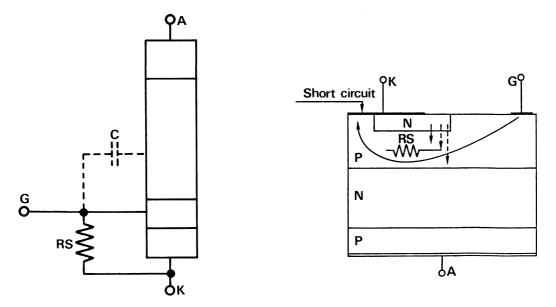

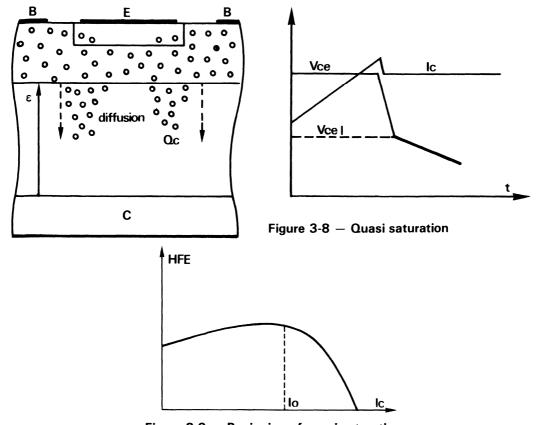

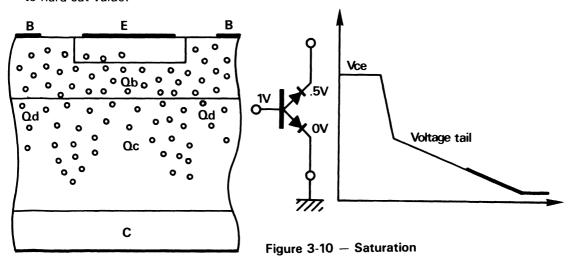

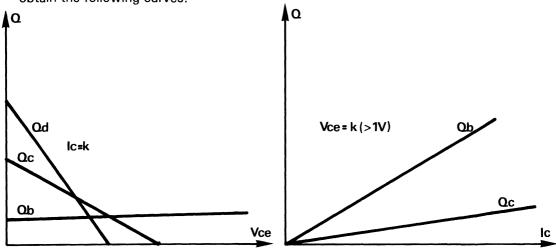

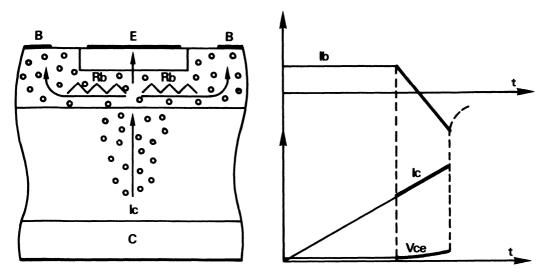

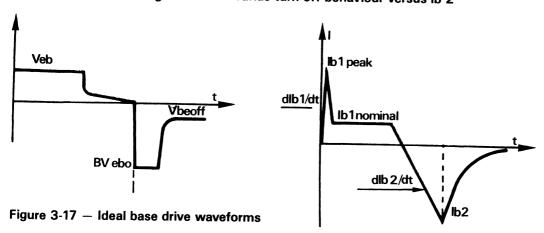

Thèse de doctorat du 3e cycle, LAAS Toulouse 1982